IDF: Auf dem Weg zum integrierten Opto-Chip

Intel baut optisch/elektrischen Wandler aus Silizium

Bereits seit über zwei Jahren arbeitete Intel an der optischen Vernetzung von Chips auf Halbleiter-Basis. Diesem Ziel ist man jetzt einen Schritt näher gekommen: Der erste opto-elektrische Wandler, der die Lichtsignale wieder in Strom wandelt, funktioniert. Als Nächstes steht die Integration mit Prozessoren auf dem Programm.

IDF: Silicon Photonics

Wie Intel-Fellow Mario Paniccia, Leiter des Photonics Technology Lab, am Vortag des IDF in San Francisco erklärte, waren für den "Photodetector" einige Klimmzüge nötig. Infrarotes Licht ist für Silizium nämlich transparent - also musste ein anderes Material als bei einer Solarzelle her, um die Lichtsignale wieder in Strom zu überführen. Dieser Vorgang steht am Ende der optischen Signalübertragung und ist notwendig, um die weiterhin elektrisch arbeitenden Chips mit den Daten zu füttern.

IDF: Silicon Photonics

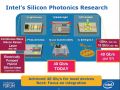

Bereits vor einem Jahr hatte Intel den ersten Hybrid-Laser vorgeführt, der sich rein mit Methoden der Halbleiterfertigung herstellen lässt. Zwar existieren, unter anderem für Gigabit-Netzwerke, schon kommerzielle Anwendungen für optische Signalübertragung, die nötigen Bausteine lassen sich jedoch noch nicht in einem siliziumbasierten Element integrieren. Das ist jedoch das Ziel von Intels Forschung im Bereich der "Silicon Photonics", um die Kosten zu senken und die Massenfertigung zu ermöglichen.

IDF: Silicon Photonics

Die gesamte Übertragungskette stand bisher, nur die Rückführung in Elektrik war noch nicht integretionsfähig. Den dafür nötigen Baustein stellte Paniccia jetzt vor. Der Wandler ist aus Silizium gebaut, auf das Germanium aufgebracht wurde. Es reagiert auch mit Infrarot-Licht und setzt dabei Elektronen frei. Das Hauptproblem war, dass der Atomabstand im Kristallgitter bei Germanium rund 4 Prozent größer ist als bei Silizium, weshalb Intel auf "Strained Silicon", also gestreckte Gitter für den Halbleiter zurückgriff.

IDF: Silicon Photonics

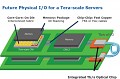

Ein einzelner der Photo-Detektoren kann 40 Gigabit pro Sekunde übertragen. Um den erstrebten Terabit-Chip zu erreichen, sind weiterhin 25 Bausteine nötig - sie sollen sich aber auf einem Baustein zusammenfassen lassen. Durch den Bau mit Halbleiter-Methoden sollen die optischen Bausteine sich auch im Sandwich-Verfahren mit einem Many-Core-Prozessor wie dem Projekt Polaris verbinden lassen. Die optische Verbindung von mehreren Prozessoren mit TeraFLOPS an Rechenleistung steht derzeit für Intel im Zentrum der Forschung an Silicon Photonics, nicht so sehr die Erhöhung der Übertragungsgeschwindigkeit von Ethernet-Netzen. Dennoch lassen sich die neuen Bauweisen der Chips theoretisch auch dort einsetzen.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

mit komma ist das doch ok!?

kt

denke ich auch, aber war wohl ein langer tag..

Interessante Technik. Auf Folie 4 macht der Satz "Future Physical I/O for a Terascale...