Neoverse V1/N2: ARMs Server-CPUs sollen Performance verdoppeln

Von 64 auf 128 Kerne, alternativ verdoppelte Ausführungseinheiten: Mit Neoverse V1/N2 legt ARM die Messlate für künftige x86-CPUs hoch.

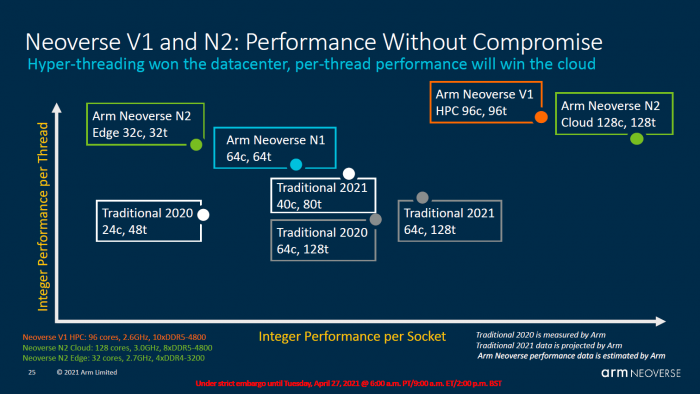

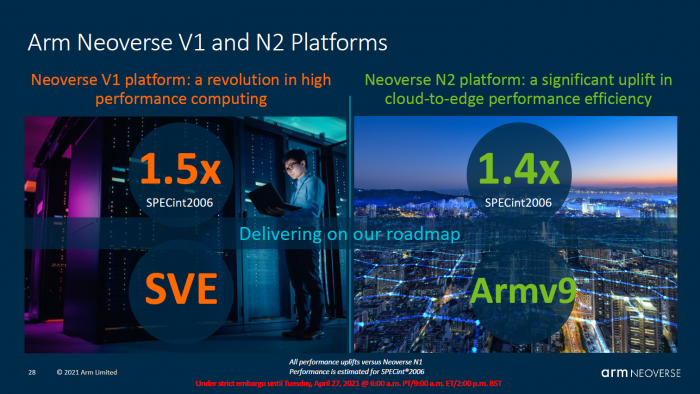

ARM hat weitere Details zu den Neoverse V1 und Neoverse N2 für Server sowie Supercomputer mitgeteilt: Die im September 2020 angekündigten CPU-Designs sollen aktuelle x86-Prozessoren deutlich überholen, egal ob bei der Sockel- oder der Thread-Performance. Hinzu kommen weitere Partner für ARM-Server.

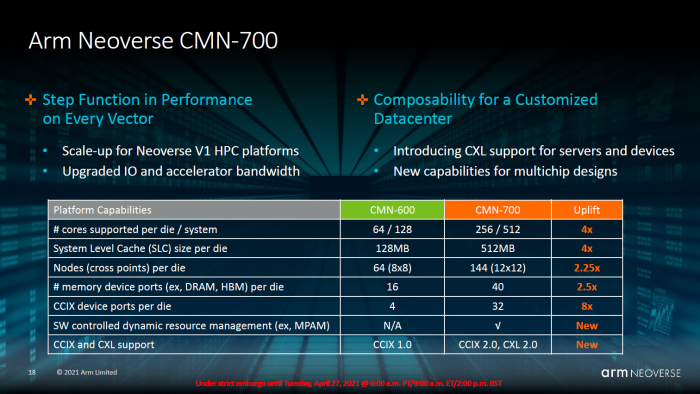

Basis beider Neoverse-Ableger sind neue CPU-Kerne, außerdem kommt das CMN-700 dazu, um diese zu verknüpfen. Dieses Coherent Mesh Network unterstützt bis zu 256 Cores pro Die, doppelt so viele wie das CMN-600 von Neoverse N1 (Ares). Der SLC (System Level Cache) wurde von 128 auf 512 MByte vervierfacht, außerdem gibt es 40 statt 16 Ports für Speicher wie DDR5, HBM2(E) oder HBM3.

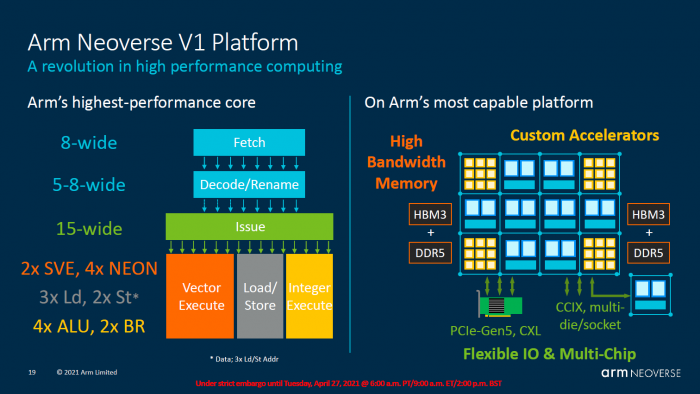

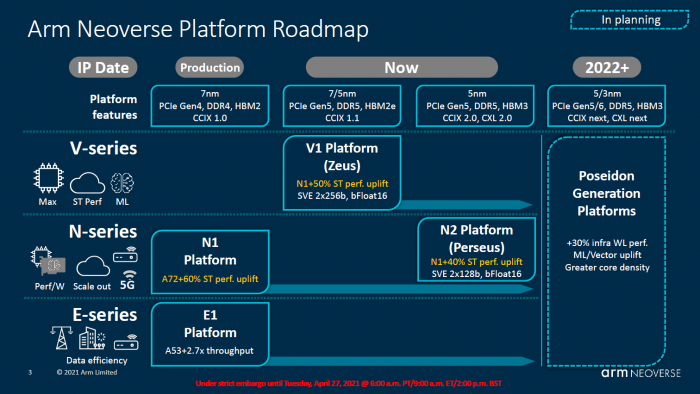

Bei Neoverse V1 (Zeus) sieht ARM neben zehn DDR5-4800-Controllern bis zu 96 Kerne mit ARMv8.4 vor, zumindest mit traditioneller Luftkühlung - mit höherer Verlustleistung und wassergekühlt können es auch mehr sein. Verglichen mit bisherigen Neoverse N1, bekannt von AWS' Graviton2 und Amperes Altra, sind die CPU-Kerne deutlich breiter gestaltet worden.

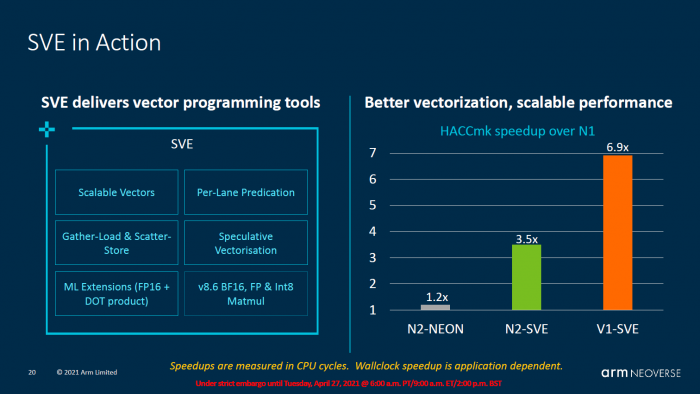

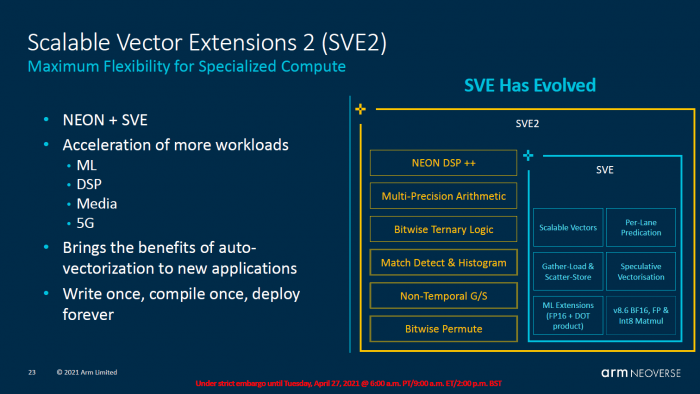

Die Scalable Vector Extension (SVE) hält Einzug

Die Fetch-Stufe wurde 8- statt 4-fach ausgelegt, der Decoder schafft fünf bis acht statt vier Instruktionen und der Dispatcher hat 15 statt 8 Ports. Im Integer-Bereich gibt es vier statt drei ALUs und zwei Branch-Einheiten statt einer. Die Neon-128-Bit-Gleitkomma-Pipelines wurden von zwei auf vier verdoppelt, auch sind zwei SVE-256-Bit-Pipes für Vector-Berechnungen vorhanden.

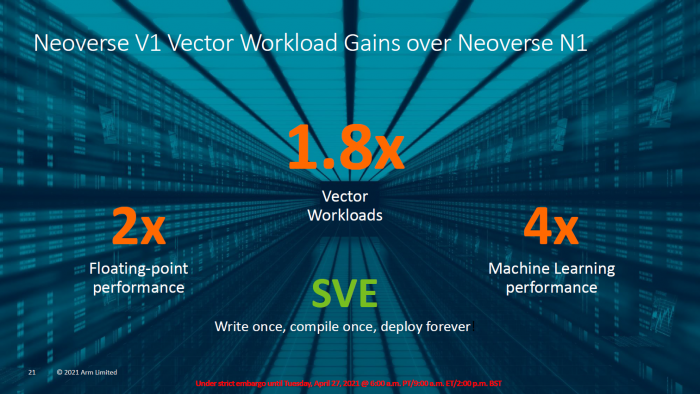

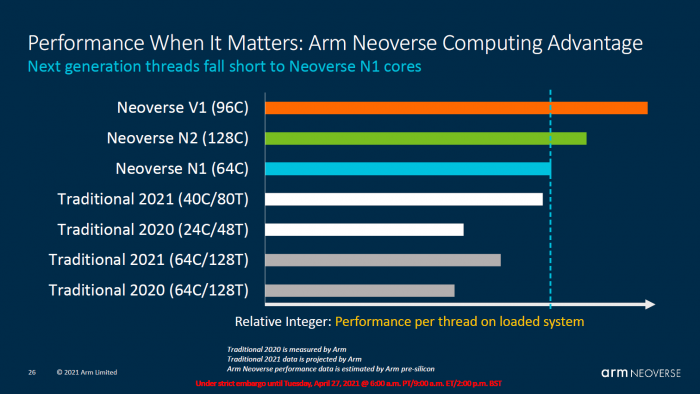

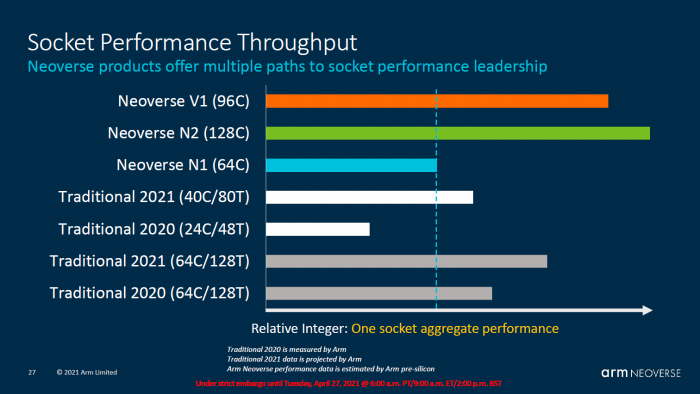

ARM spricht beim Vergleich eines Neoverse N1 mit 64C und eines Neoverse V1 mit 96C von der doppelten Float- sowie Vector-Performance, die Geschwindigkeit bei maschinellem Lernen soll sich dank Bfloat16 (BF16) sowie INT8-2x2-Matrix-Multiplikation vervierfacht haben und die Leistung pro Kern/Takt (IPC) um 50 Prozent steigen. Auch gegen Intels Ice Lake SP mit 40C/80T und AMDs Epyc 7003 mit 64/128T soll Neoverse V1 exzellent abschneiden und zumindest bei der Integer-Leistung klar vor der x86-Konkurrenz liegen.

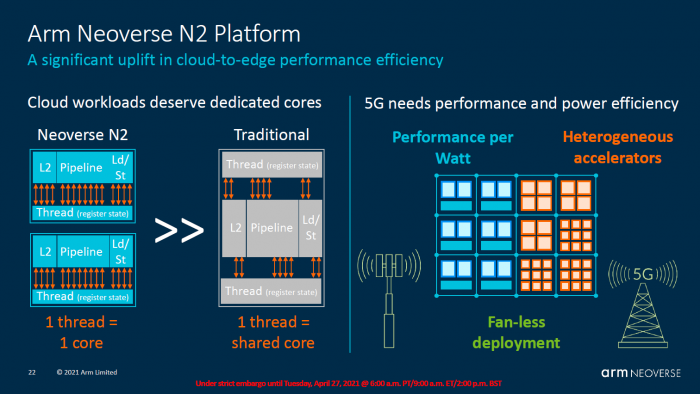

Bei Neoverse N2 (Perseus), das erste ARMv9-Design, lassen sich die Briten hinsichtlich der Architektur noch nicht in die Karten schauen. Hier sind typischerweise 128 Kerne geplant, also doppelt so viele wie bei Neoverse N1, und acht DDR5-4800-Controller. Da wundert es wenig, dass sich die Sockel-Performance verglichen mit Neoverse N1 ebenfalls verdoppeln soll. Pro Kern/Thread nennt ARM immerhin 40 Prozent Leistungszuwachs bei gleichem Takt (IPC); diverse Beschleuniger lassen sich per CXL (Compute Express Link) anbinden.

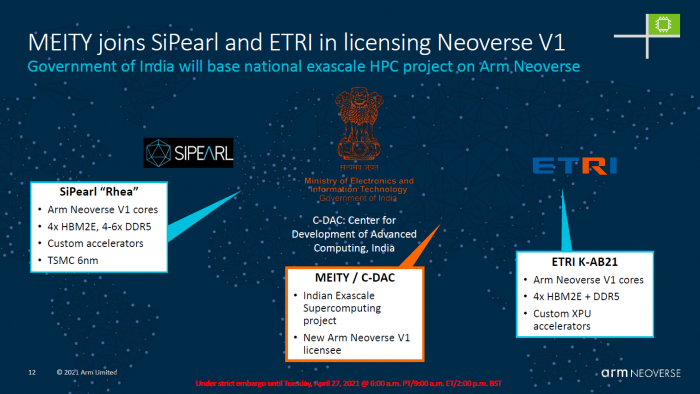

Neben der reinen Geschwindigkeit sind das Software-Ökosystem und die Unterstützung der Partner wichtig: Eines der ersten Designs mit Neoverse V1 ist SiPearls Rhea, die europäische Supercomputer-CPU mit 72 Kernen und HBM2E-Speicher. In Südkorea arbeitet das ETRI (Energy Technology Research Institute) am K-AB21, einem AI-Beschleuniger mit HBM2E- plus DDR5-Speicher.

Hinzu kommt ein noch nicht näher benanntes Design des C-DAC (Centre for Development of Advanced Computing) in Indien, hinter dem das staatliche MEITY (Ministry of Electronics and Information Technology) steht. Das erste N2-Design für neue Octeon-CPUs stammt von Marvell.

Bezüglich der aktuellen N1-Plattform teilte ARM mit, auch hier mittlerweile mehr Partner zu haben. Dazu zählen Alibaba, Cloudflare, Oracle und Tencent.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

Du kannst du IPC nur relativ zwischen den beiden Generationen angeben.

Leider hatte die EMEA-Presse keinen entsprechenden Deep Dive erhalten, wir haben das aber...

Musst warten bis Partner das umgesetzt haben - kannst dir aber Neoverse N1 als AWS...

Jedes Marketing behauptet ihre CPU ist die beste und 100x schneller als die Konkurrenz...