Apple Silicon: Hybrid-Speicher-Prozessor für Macbooks

Künftiges Apple Silicon könnte Chiplet-Stacking nutzen, um zwei Sorten von DRAM für mehr Performance und Effizienz anzubinden.

Bei Apple wird darüber nachgedacht, kommendes Apple Silicon mit einem hybriden Speichersubsystem auszustatten: Statt nur eine DRAM-Sorte zu verwenden, könnte Apple zwei Varianten an den Prozessor ankoppeln. Das würde die Leistung und die Effizienz des Konstrukts verbessern, weshalb im Patentexplizit von mobilen Geräten - ergo Macbooks - die Rede ist.

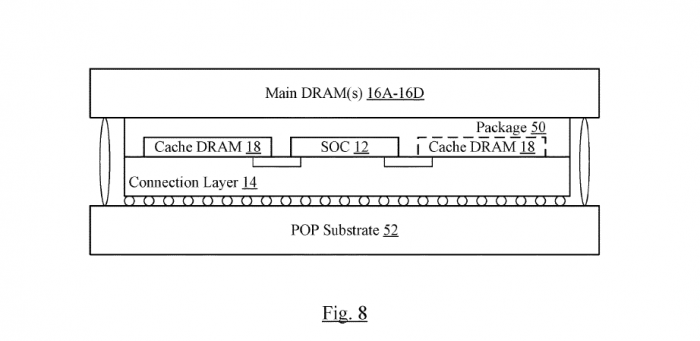

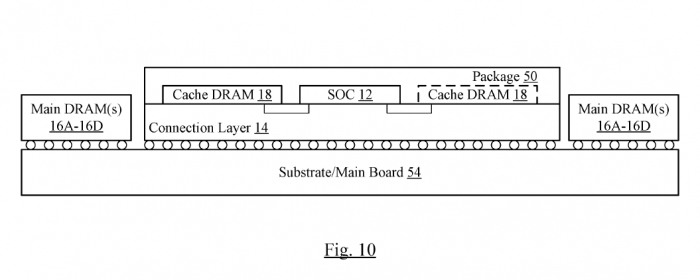

Beim aktuellen M1-Chip (Test) setzt Apple auf ein SoC, das sich zusammen mit LPDDR4X-Speicher auf einem Package befindet. Das 2016 eingereichte Patent hingegen enthält Darstellungen von Chiplet-Designs, bei denen mit 2.5D- und 3D-Stacking gearbeitet wird. Wichtig ist dabei, dass der Prozessor über hybriden Speicher verfügt.

Der Cache-DRAM hat wenig Kapazität, aber eine sehr hohe Transferrate, und der Main-DRAM sichert viele Daten, jedoch mit geringerer Geschwindigkeit. Möglich wird das durch Stacking, sodass der Speicher entweder neben (2.5D) oder über (3D) dem Prozessor platziert wird. Apples Zeichnungen zeigen, dass der Cache-DRAM gestackt und der Main-DRAM als PoP (Package on Package) auf oder regulär neben dem SoC sitzt, sprich auf Träger oder dem Mainboard.

Welche DRAM-Sorten hierbei verwendet werden sollen, darüber enthält das Patent wie üblich keine Informationen. Ein grundlegend vergleichbares Design war Intels Crystalwell, ein Laptop-Chip der Haswell-Generation. Dieses Design hatte 128 MByte schnellen eDRAM-Speicher als L4-Cache mit 102 GByte/s auf dem Package und konnte zusätzlich auf 8 GByte verlöteten DDR3L-RAM mit 25,6 GByte/s zugreifen. Lange war Apple einer der wenigen Kunden, die Intels spezielle Iris-Modelle mit eDRAM nutzen.

Es ist liegt nahe, dass Apple das hybride Speichersubsystem für das eigene Apple-Silicon umsetzen könnte. Die M-Chips für etwa ein Macbook Pro würden dann zwei DRAM-Pools aufweisen, einen zugunsten der Performance und einen für die Kapazität. Diese Kombination verbessert überdies die Effizienz, da lokal in Caches vorgehaltene Daten weniger Energie benötigen als diese aus dem Hauptspeicher zu laden.

Designs mit multiplen DRAM-Pools sind zwar eine alte Idee, die Umsetzung per Chiplet-Stacking hingegen ist relativ neu. Bei Intels Knights Landing waren es Hybrid Memory Cubes (HMC) mit DDR4, das kommende Ponte-Vecchio-Design für Supercomputer verbindet Cache-Tiles mit HBM2-Stacks.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

ein großer Stack HBM ist vermutlich so teuer wie ein ganzer M1 in der Herstellung...