Power10: IBMs Cloud-CPU hat dreifache Performance

Wenige starke Kerne und zwei Chips kombiniert: Der Power10 ist ein mächtiges CPU-Design, zumal IBM auch DDR5 integriert.

IBM hat den Power10 vorgestellt, einen für Cloud-Server gedachten Prozessor. Mit drastisch überarbeiteten CPU-Kernen, einem Dual-Chip-Ansatz und doppelt so vielen Speicherkanälen soll der Power10 die dreifache Geschwindigkeit des bisherigen Power9 erreichen.

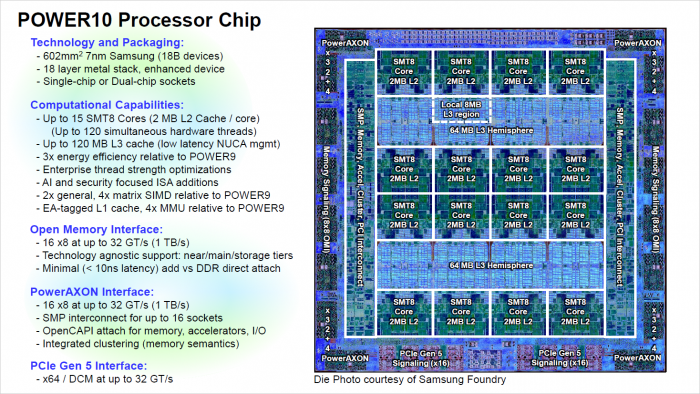

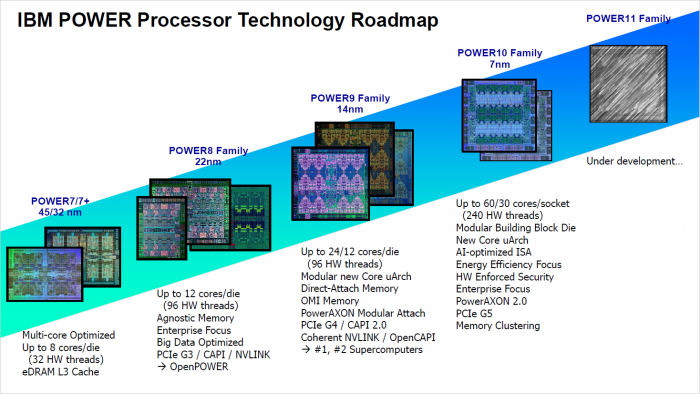

Technische Basis des Power10 ist ein Die mit 602 mm² Fläche, welches 18 Milliarden Transistoren beinhaltet. Für die Fertigung nutzt IBM das 7LPP-Verfahren von Samsung Foundry, also 7 nm mit extrem ultravioletter Strahlung (EUV). Zum Vergleich: Der Power9 kommt auf 693 mm² bei 8 Milliarden Transistoren und wurde mit Globalfoundries 14HP hergestellt. Die dazugehörige Fab 10 in East Fishkill im US-Bundesstaat New York gehörte einst IBM, wurde aber 2014 an Globalfoundries verschenkt.

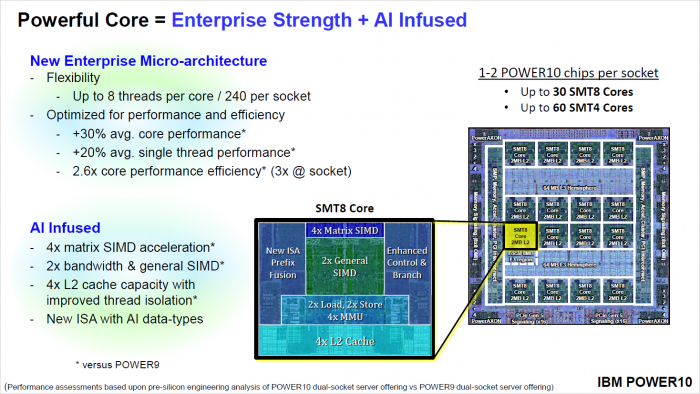

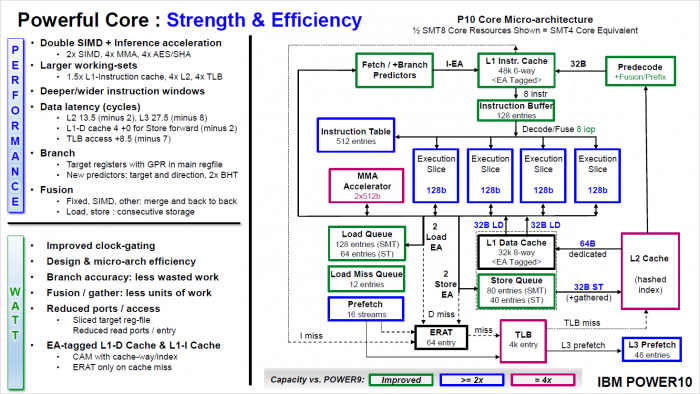

Während der Power9 noch 12 Kerne mit SMT8 oder 24 Kerne mit SMT4 aufwies, sind es beim Power10 physisch 8 Kerne mit SMT8 oder 16 Kerne mit SMT8. Freigeschaltet sind davon zugunsten der Chip-Ausbeute (Yield) allerdings nur 15, weshalb die Anzahl der logischen Cores von 96 auf 60 sinkt - allerdings nutzt IBM beim Power10 zwei Dies für 120 Threads. Die einzelnen Kerne wurden signifikant verbessert, Big Blue spricht von 30 Prozent mehr Leistung. Um dies zu erreichen, kommen ein Drittel mehr Instruktionen aus dem L1I-Puffer, es gibt eine schnellere Sprungvorhersage, doppelt so breite SIMD-Einheiten (128 Bit statt 64 Bit) und größere Buffer/Caches mit kürzeren Latenzen samt doppelter Bandbreite.

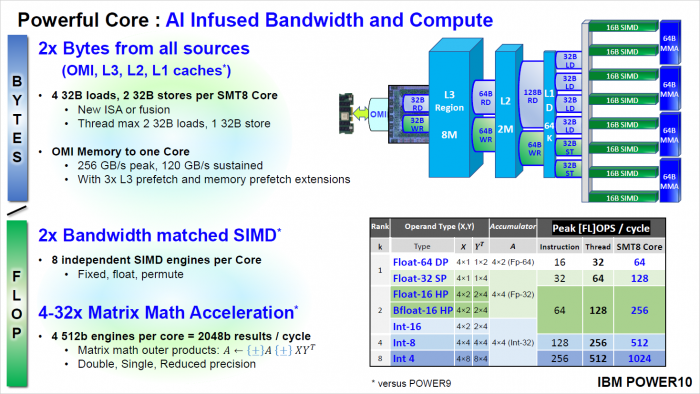

Komplett neu ist ein Block für Matrizen-Multiplikationen, diese werden für Inferencing, also das Ausführen eines bereits trainierten neuronalen Netzes verwendet. Dieses Inferencing kann mit doppelter Genauigkeit (FP64), mit einfacher Präzision (FP32), mit halber (BF16 sowie FP16) und mit reduzierter (INT8 sowie INT4) durchgeführt werden. Ein SMT8-Kern schafft dank acht 512-Bit-Einheiten bis zu 1.024 Ops pro Takt. Verglichen zum Power9 erhöht sich so die Inferencing-Geschwindigkeit, um den Faktor 10x (Resnet-50 mit FP32) über 15x (Resnet-50 mit BF16) bis 20x (Resnet-50 mit INT8).

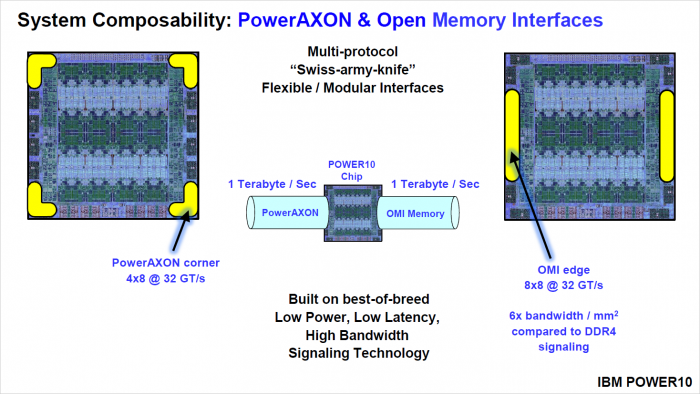

Jeder Chip hat 16 Interfaces für initial 4 TByte an DDR4-3200, die Bandbreite liegt somit bei 410 GByte/s. Der ursprüngliche Power9 SO (Nimbus) kommt auf 120 GByte/s, der spätere Power9 SU (Cumulus) auf 230 GByte/s und der nachgeschobene Power9 AIO (Axone) auf 350 GByte/s. Erneut verwendet IBM das Open Memory Interface (OMI), um den Speicher anzubinden. Neben DDR4 soll später auch DDR5 eingesetzt werden, prinzipiell denkbar sind zudem sogenannte OMI-Differential-DIMMs mit High Bandwidth Memory für 800 GByte/s oder nicht flüchtiger Storage Class Memory. Per Power-Axon-2.0-Schnittstelle werden Beschleuniger wie ASICs oder FPGAs kohärent angebunden (Open CAPI).

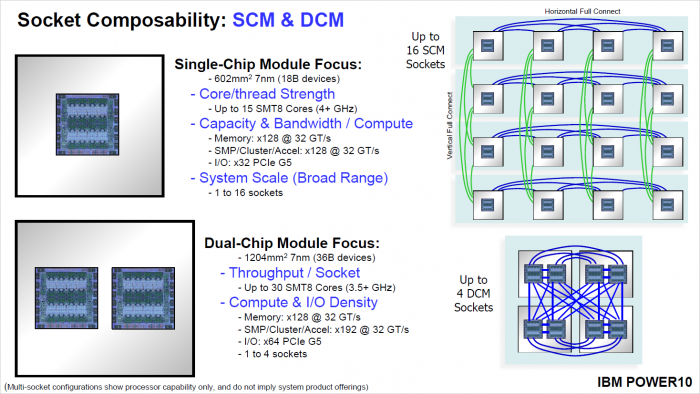

Dank der überarbeiteten Architektur und dem 7LPP-Verfahren konnte laut IBM die Leistung pro Watt um den Faktor 2,6x gesteigert werden. Daher bietet Big Blue den Power10 als SCM (Single Chip Module) mit über 4 GHz sowie 32 PCIe-Gen5-Lanes und als DCM (Dual Chip Module) mit über 3,5 GHz sowie 64 PCIe-Gen5-Lanes an. Weil so zwei Dies in einem Package rechnen, liefert der Power10 (DCM mit 30C/240T) die dreifache Performance des Power9 (12C/96T) - egal ob Enterprise, Float oder Integer. Einzig die effektive Speicherbandbreite wurde nur verdoppelt, mit DDR5 soll diese jedoch vervierfacht werden.

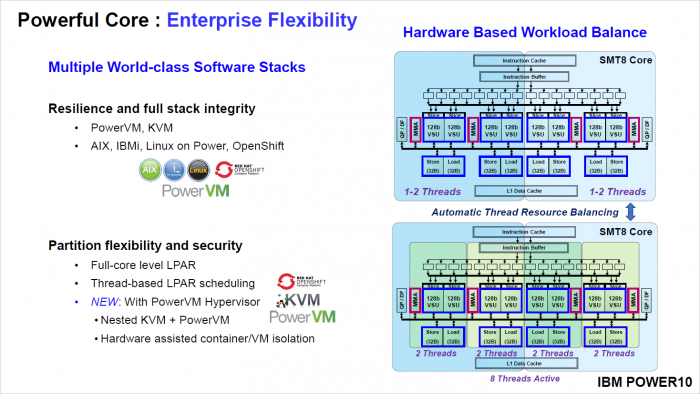

Als SCM-Variante bietet IBM den Power10 für bis zu 16 Sockel an, in der DCM-Variante ist bei vier Fassungen bereits Schluss. Die CPUs unterstützen AIX, IBMi, Linux und OpenShift, wobei die Betriebssysteme sowie die Container-Plattform parallel auf dem PowerVM-Hypervisor laufen können. Erste Systeme mit Power10 erwartet IBM im zweiten Halbjahr 2021.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

Danke

Schauen wir mal bei Verfügbarkeit ^^

15 Cores mit SMT8 oder 30 Cores mit SMT4, je nach Einstellung bzw das Doppelte mit Multi...