SSDs: Intel arbeitet an 144-Schicht-Speicher und 5-Bit-Zellen

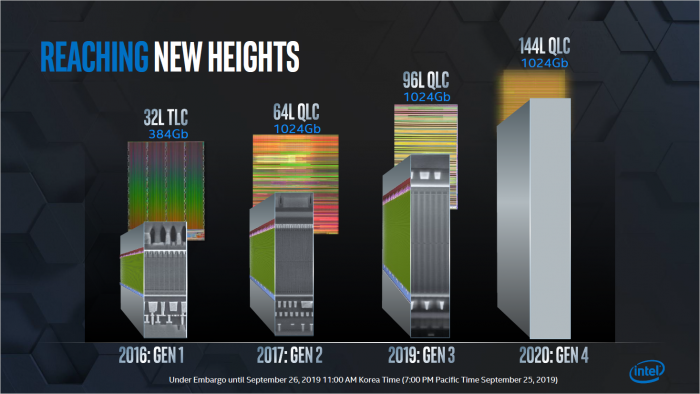

2020 will Intel seine vierte 3D-NAND-Generation veröffentlichen, sie basiert auf 144 Flash-Speicher-Schichten. Zukünftig sollen damit auch Zellen mit 5 Bit (PLC) umgesetzt werden. Zudem gibt es Neuigkeiten zu Optane-Modulen und -SSDs mit Intels nicht flüchtigem 3D-XPoint-Speicher.

Intel hat auf seinem Storage Day im südkoreanischen Seoul einen Ausblick auf kommende Speichertechnologien und -produkte gegeben: Nach der Trennung von Micron und dem Ende des IMFT-Joint-Ventures entwickeln beide Hersteller eigene Designs. Vor Ort sprach Intel über ein Entwicklungszentrum für Optane-basierte Module und SSDs in New Mexico, über 144-schichtigen Flash-Speicher und über den Plan, künftig auch 5 Bit pro Zelle zu verwenden.

Bei Rio Rancho im US-Bundesstaat New Mexico wurde eine sogenannte Tech Dev Line für die Fab 11X gebaut, dort wird der nicht flüchtige 3D-Xpoint-Speicher für Optane-Produkte weiterentwickelt. Dazu gehört auch Barlow Pass, das ist der Codename für die zweite Generation des Optane DC Persistent Memory für Xeon-CPUs. Ob für die Chips auf den Modulen noch immer ein 20-nm-Verfahren und 128 GBit Kapazität pro Die verwendet werden, wollte Intel nicht sagen. Dafür gab der Hersteller bekannt, dass Microsoft auch 8-Sockel-Systeme mit 18 TByte anbieten will. Die Azure-Cloud-Systeme nutzen pro CPU offenbar sechs Kanäle mit je drei DIMMs mit 128 GByte.

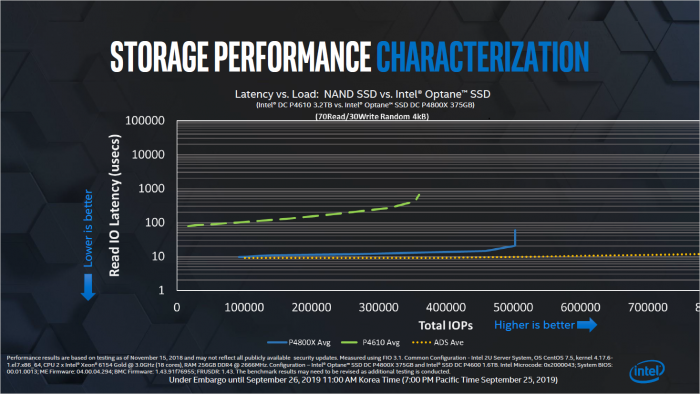

Zudem wurde mit Alderstream eine Optane-SSD beworben, die bei sehr geringer Latenz weit über 700.000 Input-/Output-Operationen pro Sekunde erreichen soll. Die bisherige Optane-SSD P4800X (Coldstream) schafft in diesem Szenario nur etwa 500.000 IOPS und eine P4610 mit Flash-Speicher bei über zehnfacher Latenz keine 400.000 IOPS. Wo Intel den 3D-Xpoint nach der Trennung von Micron fertigen will, ließ der Hersteller offen - denn die Fab 2 in Lehi im US-Bundesstaat Utah gehört nun dem ehemaligen Partner.

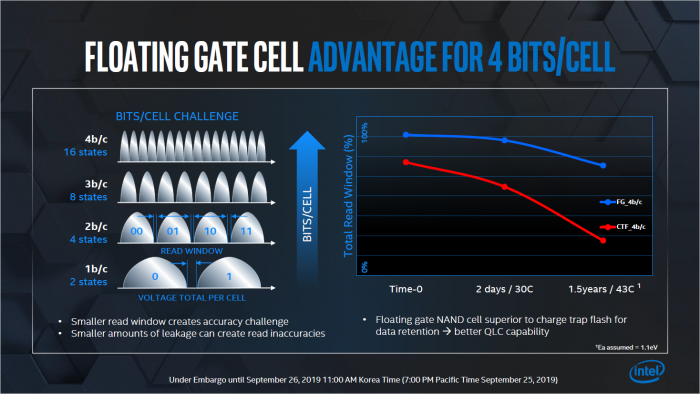

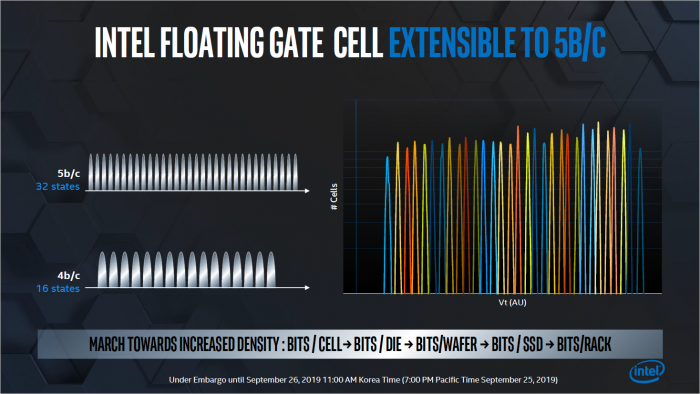

Der kommende 3D-NAND v4 ist eine Eigenentwicklung von Intel, hier werden 144 Schichten (bestehend aus wenigstens zwei Stacks) mit 4-Bit-Zellen für 1.024 GBit pro Chip verwendet. Der Logikteil sitzt wie gehabt unter dem Flash-Array und Intel nutzt erneut Floating-Gate-Zellen. Verglichen mit dem Charge-Trap-Ansatz, wie ihn etwa Samsung beim V-NAND v6 integriert, sieht Intel bei der Floating-Gate-Technik bessere Möglichkeiten, das Zeitfenster zum Auslesen von Daten über einen längeren Zeitraum hin stabil zu halten. Bei 4 Bit sind bereits 16 Spannungszustände notwendig, für Zellen mit 5 Bit (Penta Level Cells) dann gleich 32. Wann PLC-Speicher erscheint, gilt es abzuwarten.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

Wohl seit den ersten. Die X25m hatte damals im vergleich zu anderen bereits sehr hohe OP...

Es gibt ja auch die Notwendigkeit zur Archivierungen "kleinerer" Datenmengen - z. B...