Agilex: Intels 10-nm-FPGAs nutzen Chiplet-Design

Die Altera-Tochter legt nach: Die Agilex-Generation der programmierbaren Schaltungen kann mit PCIe Gen5 umgehen, zudem binden die FPGAs eine Vielzahl an Speichertypen und sie sind Cache-kohärent zu Intels Xeon-Prozessoren. Vor allem aber ist das Design flexibel erweiterbar.

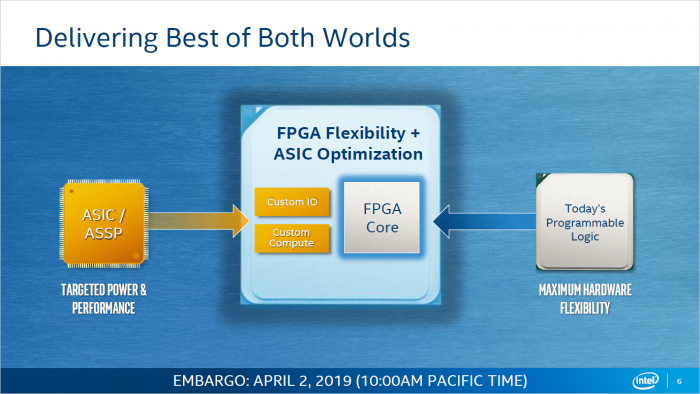

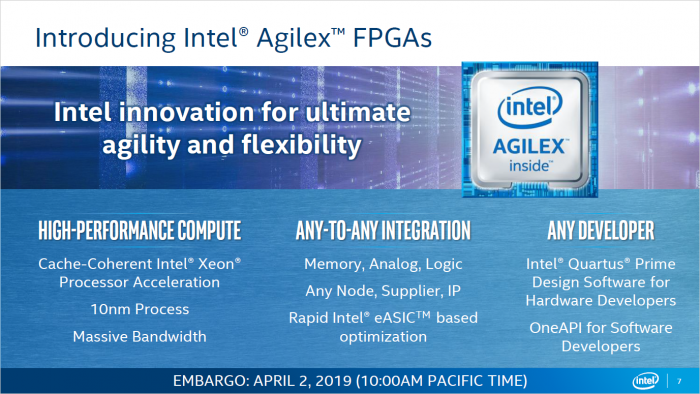

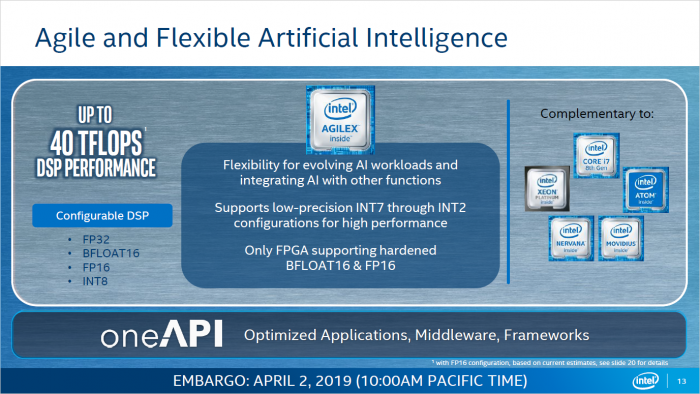

Auf die von Altera entwickelten Stratix-FPGAs folgen die programmierbaren Schaltungen namens Agilex der Programmable Solutions Group, wie der Hersteller nach der Übernahme durch Intel mittlerweile heißt. Die Agilex sind Intels erste FPGAs, welche im hauseigenen 10-nm-Verfahren gefertigt und bereits im dritten Quartal 2019 zumindest an Partner verteilt werden sollen. Gedacht sind die Chips unter anderem für künstliche Intelligenz, weshalb der Aufbau sehr flexibel und eine Hardware-Unterstützung für Googles bfloat16-Format vorhanden ist.

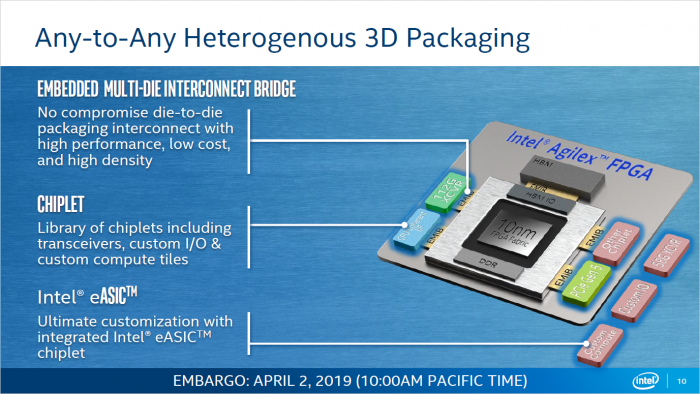

Die Agilex selbst sind 10-nm-FPGAs, welche bis zu 40 Teraflops theoretische Rechenleistung bei halber Genauigkeit (Half Precision, FP16) aufweisen sollen. Daneben beherrschen die programmierbaren Schaltungen auch noch FP32 sowie INT8, überdies sollen eher untypische Formate wie INT7 oder INT2 integriert sein. Alle Agilex-Modelle unterstützen DDR4-Arbeitsspeicher und einige haben noch ein Interface für DDR5 sowie High Bandwidth Memory und damit eine extrem hohe Bandbreite. Die reine Geschwindigkeit alleine hilft aber wenig, wenn das Drumherum nicht passt - und das ist bei den Agilex wörtlich zu nehmen, denn Intel verknüpft die FPGAs mit allerhand Chiplets.

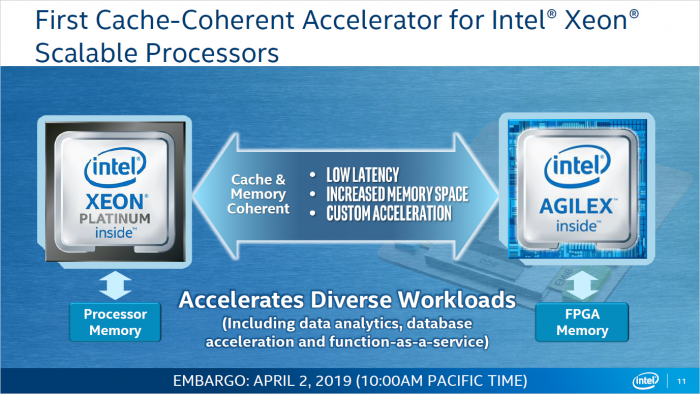

So nennen Hersteller den Ansatz, mehrere Dies zu kombinieren, wobei Intel auf die eigene EMIB-Technik setzt. Mit der Embedded Multi (Die) Interconnect Bridge verzahnen die Agilex-FPGAs nicht nur den HBM-Speicher, sondern stellen auch eine Cache- und Speicher-Kohärenz zu Xeon-Prozessoren her, sofern diese über PCIe-Lanes samt UPI-Protokoll (Ultra Path Interconnect) mit den programmierbaren Schaltungen verbunden sind. Diese Datenparität hilft, die Leistung zu steigern, weil die CPU und der FPGA die gleichen Daten bearbeiten. Der Vorläufer dieser Umsetzung ist der Xeon 6138P, hier sitzen beide Chips - der Prozessor und der Stratix - jedoch auf einem gemeinsamen Package.

Intel selbst liefert als Chiplet neben PCIe-Gen4/Gen5-Phys auch einen Transceiver (Falcon Mesa) mit, welcher ebenfalls in 10 nm gefertigt wird und 112 GBit/s erreichen soll. Denkbar seien aber auch andere Transceiver sowie weitere Designs aus Intels Bibiothek, zudem können Partner via eASIC auch eigene Lösungen entwerfen und diese als Chiplet an die Agilex-FPGAs anbinden. Intel unterteilt die programmierbaren Schaltungen in die F-, die I- und die M-Serie, welche unterschiedliche Phys für DDR4/DDR4 sowie PCIe Gen4/Gen5 und eine abweichende Rechenleistung aufweisen.

Offenlegung: Golem.de hat auf Einladung von Intel hin am Server Workshop in Portland teilgenommen, die Reisekosten wurden gänzlich von Intel übernommen. Unsere Berichterstattung ist davon nicht beeinflusst und bleibt gewohnt neutral und kritisch. Der Artikel ist, wie alle anderen auf unserem Portal, unabhängig verfasst und unterliegt keinerlei Vorgaben seitens Dritter.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

Ja dann haben wir doch das sinnvolle Consumerszenario, wenn einfach die KI mal beim...

sorry