Prozessoren: AMD verteilt bei Zen 2 die Kerne und I/O auf mehrere Chips

Multichip-Packages gibt es bald auch bei Mainstream-CPUs: AMD packt die x86-Kerne und die Busse inklusive Speichercontroller in getrennte Chips. Das Design darf man revolutionär nennen.

Was bei allen modernen Prozessoren neben der reinen Rechenleistung der x86-Cores gefragt ist, nennt sich Bandbreite. Die Datentypen werden immer größer, und vom Speicherbus für DDR4-DRAM bis zur Verbindung von Dies untereinander - was bei Ryzen schon in der ersten Generation ein Designkniff war - muss alles schneller miteinander kommunizieren. Da ist es verwunderlich, dass AMD bei der neuen Architektur Zen 2 alle I/O-Funktionen in ein eigenes Modul auslagert.

Dieses Modul, das noch keinen Namen hat, wird aber in 14-nm-Technik hergestellt und ist somit günstiger und in größeren Stückzahlen schnell herstellbar. Die Vorteile von 7-nm-Fertigung bekommen vorerst nur die Cores, die in mehreren von AMD sogenannten Chiplets zusammengefasst werden. In den ersten Folien, die AMDs Technikchef Mark Papermaster in San Francisco zeigte, sind zwei dieser Chiplets vorgesehen. Es dürften aber auch mehr möglich sein, wahrscheinlich sind mindestens vier Cores pro Chiplet, so dass beispielsweise ein 8-Core-Ryzen aus zwei Chiplets und dem I/O-Block bestehen kann. Oder auch nur aus einem Chiplet, denn für die Rome-Epycs haben die Bausteine acht Cores in einem Die.

Diese müssen auf einem Substrat als Multichip-Package (MCP) verbunden werden. Ob dafür AMDs Fabric, das schon in Ryzen und Epyc steckt, zum Einsatz komme oder ein noch schnellerer Bus, erklärte Papermaster nicht. Da die Veranstaltung Next Horizon, auf der AMD auch andere Techniken rund um 7-nm-Fertigung vorstellt, aber erst begonnen hat, ist mit weiteren Details zur Chiparchitektur von Zen 2 zu rechnen. Er wird im Übrigen nicht der erste 7-nm-Chip von AMD werden - das sind die neuen Vega-GPUs, die noch 2018 auf den Markt kommen sollen. Zen 2 ist für die Reihen Ryzen und Epyc für 2019 vorgesehen.

Nachtrag vom 6. November 2018, 20:47 Uhr

Papermaster nannte in seinen Vorträgen doch noch einige Details zur Architektur von Zen 2 - aber nicht, wie die mindestens drei verschiedenen Dies verbunden sind.

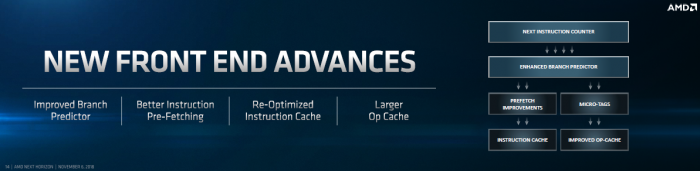

Die Veränderungen am Frontend und den Datentypen sind aber mindestens ebenso spannend. Ziel von Zen 2 ist es vor allem, die pro Takt verarbeiteten Befehle (IPC) zu steigern. Dabei haben Intels Lake-Architekturen noch immer einen leichten Vorteil. Der soll unter anderem durch einen neuen Prefetcher eingeholt werden. Diesem ist eine neue Verzweigungsvorhersage (Branch Predictor) vorgeschaltet, die wiederum von einem Befehlszähler gefüttert wird. Dieser Next Instruction Counter, dessen Name nicht viel über die Funktion verrät, dürfte in der Umsetzung wichtig werden - immerhin soll Zen 2 gegen Seitenkanalangriffe der Spectre-Klasse auch in Hardware besser geschützt werden. Für mehr Tempo soll auch ein erweiterter Micro-Op-Cache sorgen, der die dekodierten und in Einzelschritte zerlegten Befehle zwischenspeichert. Wie groß der Cache sei, sagte Papermaster nicht.

Bei der SIMD-Verarbeitung soll Zen 2 durch nun mit 256 Bit doppelt so breiten FPU-Datentypen an Tempo zulegen. Dafür gibt es auch ebenso breite Load/Store-Einheiten. Das sollte etwas zu Intel aufschließen, die mit AVX-512 - bei dann allerdings reduzierten Taktraten - für speziell angepasste Anwendungen bei SIMD immer noch führend sind. Allerdings: Von anderen AMD-Präsentationen zu den Epyc-CPUs rückschließend soll sich die FPU-Leistung von Zen 2 insgesamt verdoppeln. Dabei rechnete AMD aber wohl einen mutmaßlichen Taktvorteil schon ein.

Zur Gesamtperformance eines Zen 2 sagte Papermaster, es könne die Hälfte der Leistungsaufnahme bei gleicher Performance oder 25 Prozent mehr Rechenleistung bei gleichem Strombedarf erreicht werden. 7-nm-Technik sei nicht so effizient wie frühere Die-Shrinks. Eventuell ist dafür aber auch der I/O-Block mit 14 nm der Grund.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

Und was soll mir der Link jetzt sagen? Ich sehe da keinen direkten Bezug zu meinem Zitat...

Aus meiner Sicht war der Energiebedarf eher Nebensache. Kleinere Strukturen - kurze...

Vielen Dank für dieses inhaltlich redundante TL;DR zum Artikel ;-)

Bulldozer hatte zu wenig FPUs / SIMD Einheiten.