Xeon Skylake-SP: Das können Intels 28-Kern-CPUs mit AVX-512

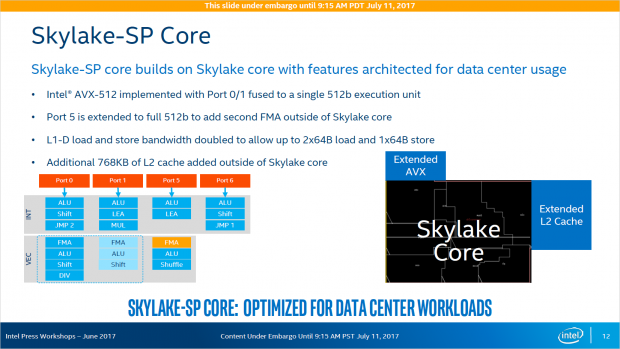

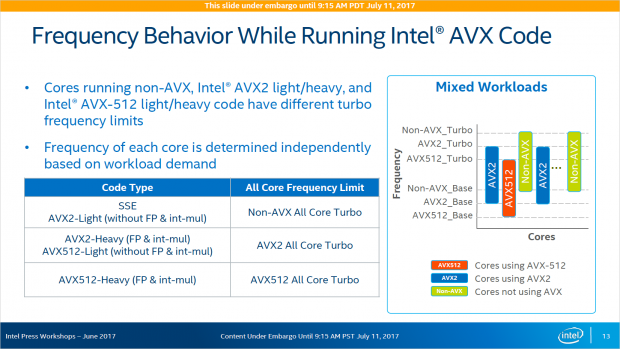

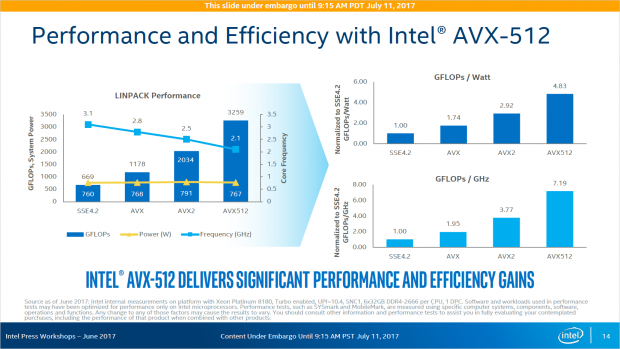

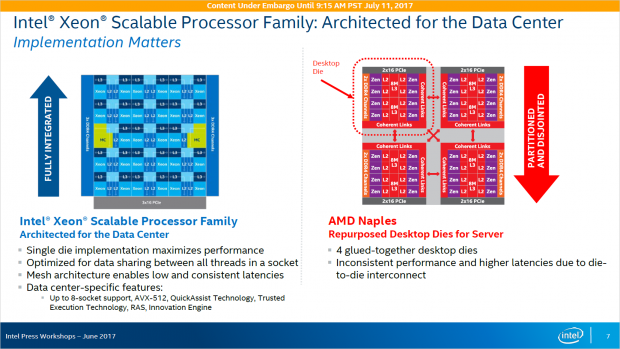

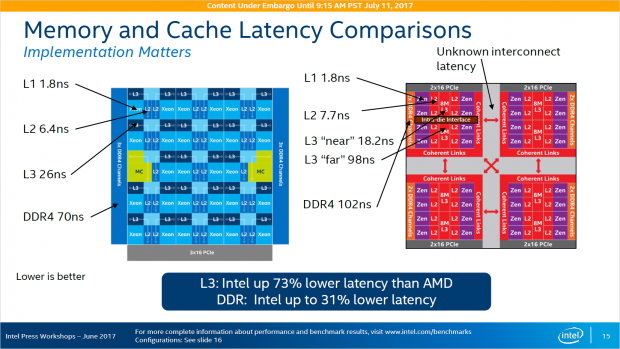

Aufgrund vieler Kerne und Speicherkanäle sind die Xeon Scalable Processors alias Skylake-SP sehr schnell. Die Server-CPUs nutzen mehrere neue Interconnects und erstmals AVX-512-Instruktionen. Amüsant war der Vergleich mit AMDs Epyc, denn der bestehe ja nur aus zusammengepappten Desktop-Chips.

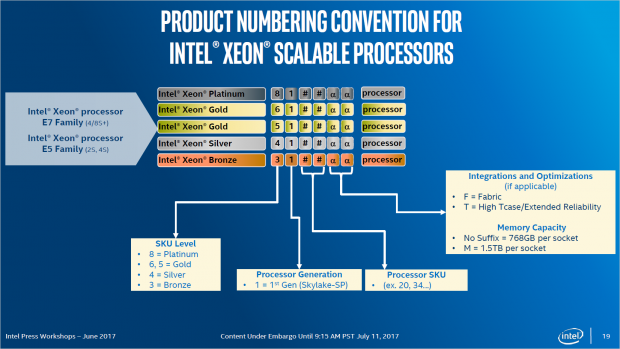

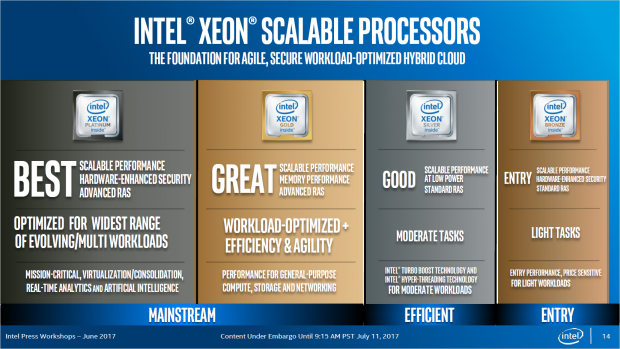

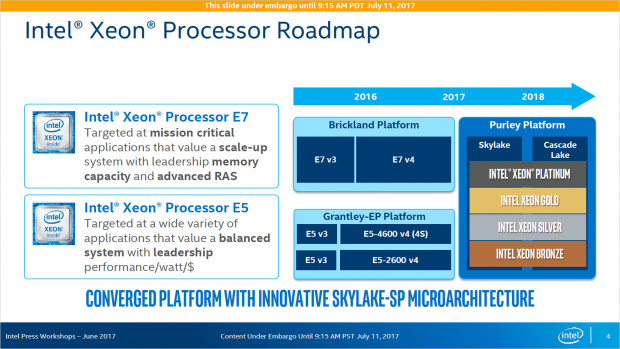

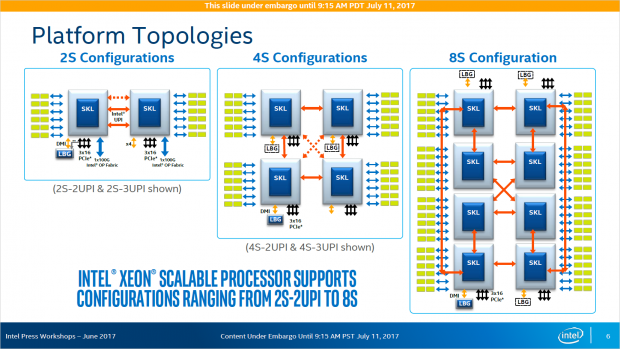

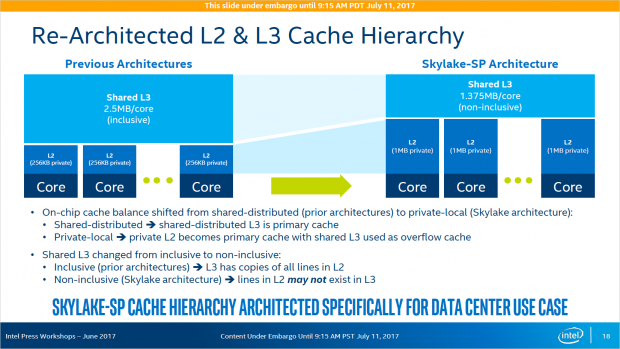

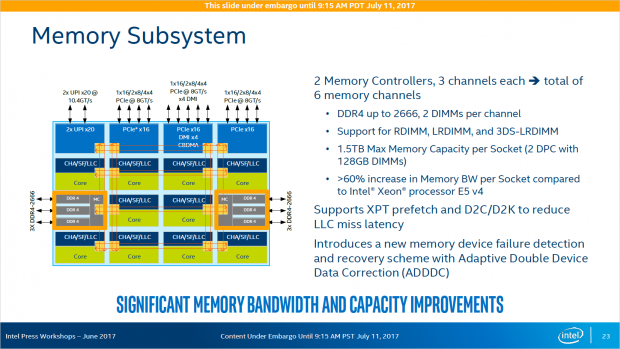

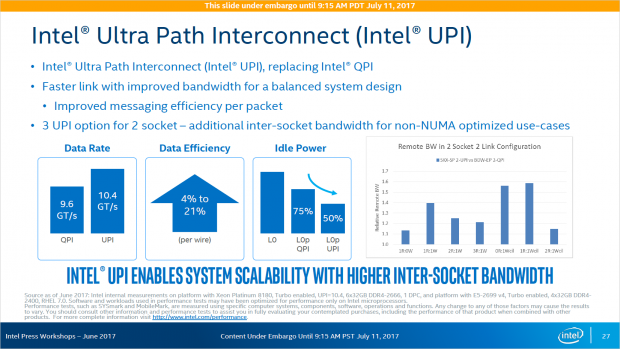

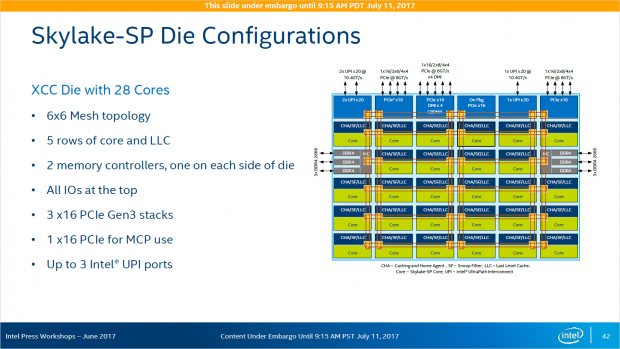

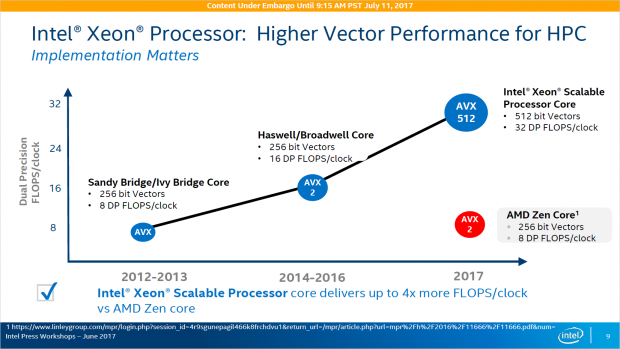

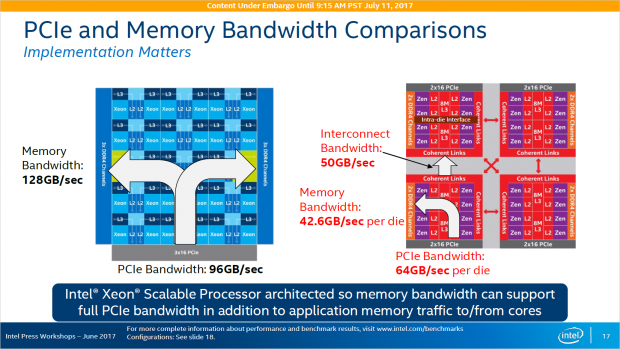

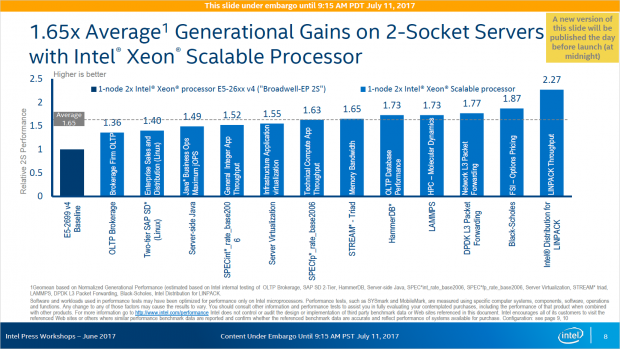

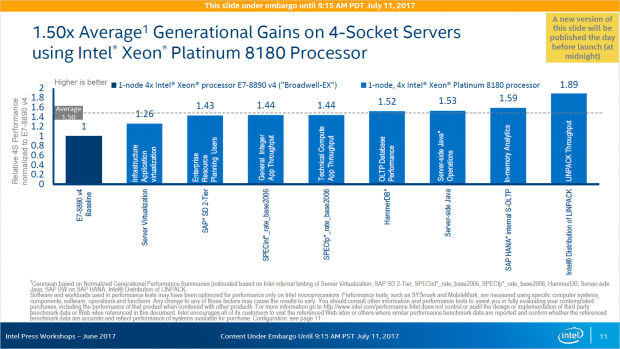

Intels neue Generation von Server-CPUs macht vieles anders als bisherige Prozessoren. Das beginnt schon beim Namen: Zuvor unterteilte der Hersteller sein Portfolio in die Xeon E5 und die Xeon E7, bei den Xeon Scalable Processors fehlt dieses Schema nun. Stattdessen verkauft der Hersteller die SP-Chips mit Platinum-, Gold-, Silver- und Bronze-Zusatz. Die technischen Änderungen bestehen aus weiteren CPU-Kernen, zusätzlichen PCIe-Gen3-Lanes, einem Mesh-Interconnect, einer anderen Cache-Topologie, einer schnelleren Inter-Sockel-Verbindung und noch allerhand mehr Neuerungen. Intel spricht bei der Purley-Plattform vom größten Data-Center-Launch seit einem Jahrzehnt.

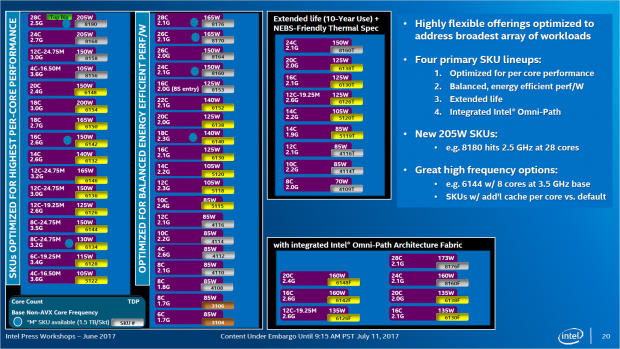

Die grundsätzliche Einteilung erfolgt in vier Leistungsklassen, die an (Edel)metalle angelehnt sind. Mit Platinum gibt es bis zu acht Sockel, bis zu 28 Kerne, DDR4-2666-Speichertakt, volle AVX-512-Geschwindigkeit und eine dreifache Verknüpfung der CPUs untereinander. Bei Gold erhalten Käufer bis zu vier Sockel und bis zu 22 Kerne, aber teils nur zwei Sockel-Links, teils halbierten AVX-512-Speed und langsameren RAM. Bei Silver und Bronze ist bei zwei Sockeln sowie 12 und 8 Kernen schon Schluss, die beiden CPU-Verbindungen sind gedrosselt, der Speicher niedriger getaktet und der Turbo fehlt.