AI-Beschleuniger: Intels Spring Crest erscheint Ende 2018

Die erste Generation von Intels Deep-Learning-ASIC ist noch nicht verfügbar, der Nachfolger ist aber bereits geplant. Spring Crest folgt auf Lake Crest; es handelt sich hierbei erneut um einen Spezialchip mit Stapelspeicher für Beschleunigerkarten.

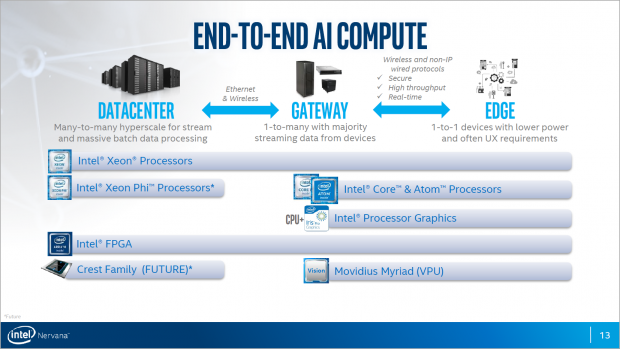

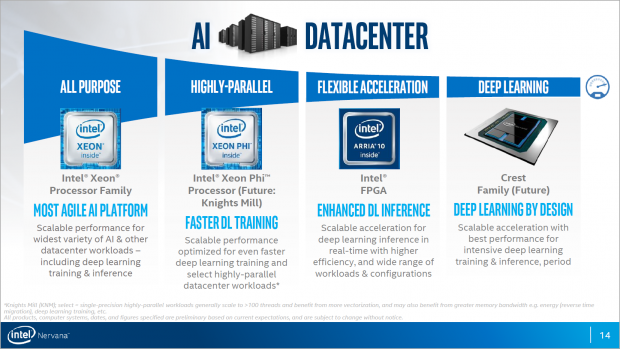

Intel hat auf dem Server-Workshop zu den Xeon SP auch über die Crest-Familie gesprochen. Diese Chips sind das Resultat der Nervana-Übernahme im Spätsommer 2016, mit der sich Intel besser im Deep-Learning-Markt positionieren möchte. Bisher hat der Hersteller zwei Varianten angekündigt, Lake Crest und Knights Crest. Erstere soll noch 2017 verfügbar sein. Beide eignen sich für die Training- und Inference-Schritte.

Lake Crest ist die alleine lauffähige Variante, es handelt sich dabei um einen ASIC (Application Specific Integrated Circuit). Der Chip ist maßgeschneidert für die Berechnung von neuronalen Netzen, die von einem Dutzend spezialisierter Processing Cluster verarbeitet werden. Die Crest-Modelle nutzen etwas, das Intel als Flexpoint-Architektur bezeichnet, die intern im Integer-Format rechnet und eine variable Genauigkeit für Matrixen-Multiplikationen unterstützt. Lake Crest verzichtet auf Caches und nutzt nur HBM2-Speicherstapel.

Ende 2018 soll mit Spring Crest der Nachfolger erscheinen, für den Intel sicher keinen fremden 28-nm-Prozess verwendet, sondern ein moderneres Fertigungsverfahren. Für Lake Crest gab Nervana vor der Übernahme eine Rechenleistung von 55 Teraops an, was schwer vergleichbar ist. Googles aktuelle TPUs schaffen 180 Teraflops bei FP16-Genauigkeit und Nvidias Tesla V100 kommt auf 120 Teraflops bei Half Precision.

Gesockeltes Crest-Modell geplant

Neben Lake Crest und Spring Crest arbeitet Intel noch an Knights Crest. Dieser Ableger kombiniert einen gesockelten und bootbaren x86-Xeon-Prozessor mit einem nicht näher erläuterten ASIC als Beschleuniger auf einem gemeinsamen Träger. Allerdings ist Knights Crest erst für 2020 geplant.

Intel gibt an, in den vergangenen Monaten viel Aufwand und Zeit investiert zu haben, um die eigene Software für verbreitete Deep-Learning-Frameworks zu optimieren. Dadurch seien massive Leistungssteigerungen erzielt worden, zuletzt durch die AVX-512-Integration in Caffe für die Xeon SP.

Offenlegung: Intel hat die Reisekosten nach Portland für Golem.de übernommen.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

Sie führt uns zu Skynet.