DLU: Fujitsu entwickelt Deep-Learning-Chips

Neben eigenen ARM-Prozessoren für den Post-K-Supercomputer arbeitet Fujitsu auch an Deep-Learning-Einheiten. Den DLUs reicht eine niedrige Integer-Präzision, weshalb die Energie-Effizienz extrem hoch ausfallen soll. Vorerst sind dedizierte Beschleuniger angedacht, später dann On-Package-Varianten.

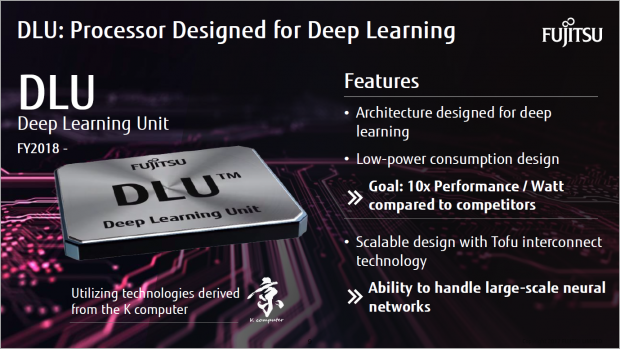

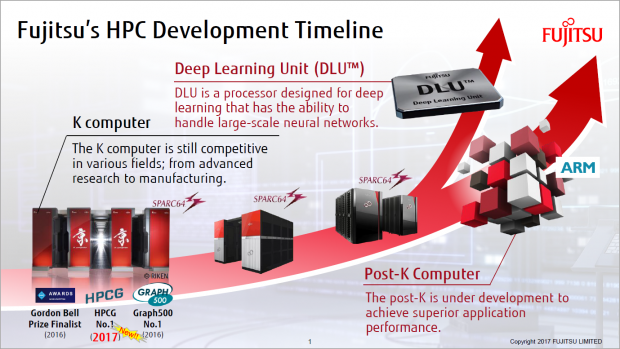

Fujitsu hat sich ausführlicher zu seinen kommenden Spezialchips für künstliche Intelligenz geäußert, die erstmals im Frühsommer 2015 öffentlich erwähnt wurden (PDF). Die als Deep Learning Units (DLU) bezeichnete Hardware soll drastisch effizienter ausfallen als die der Konkurrenz, die Japaner sprechen von Faktor zehn. Im Rahmen der International Supercomputing Conference, die im Juni 2017 in Frankfurt stattfand, sagte Fujitsus Senior Director der AI Platform Division, Takumi Maruyama, der Fokus liege auf einer geringen Rechengenauigkeit, da diese ausreichend sei (PDF).

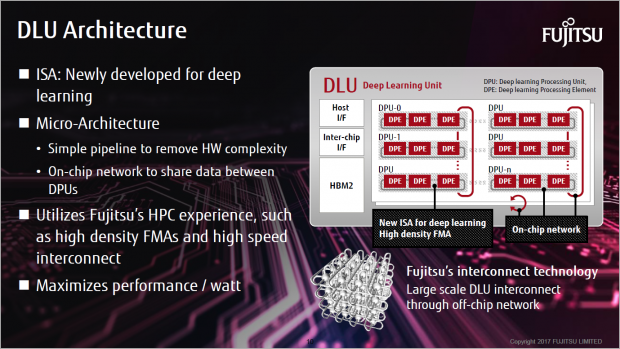

Neben einfacher (FP32) und halber Gleitkommapräzision (FP16) unterstützen die Deep Learning Units daher auch INT16 und INT8, wie es etwa bei Nvidias Tesla-Beschleunigern der Fall ist. Jeder Chip besteht aus multiplen DLUs, die per Fabric untereinander und mit HBM2-Stapelspeicher verbunden sind. Jede Deep Learning Unit weist 16 Deep Learning Elements (DLE) auf, die wiederum acht SIMD-Einheiten samt sehr großen Register Files beinhalten.

Erst dediziert, dann integriert

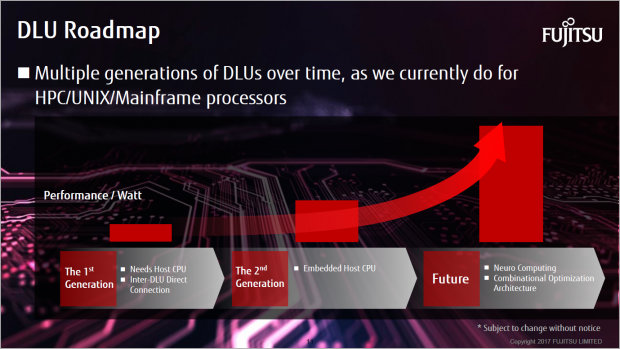

Vorerst plant Fujitsu, die Spezialchips auf Beschleunigerkarten zu montieren, die mit dem Tofu-Interconnect miteinander sowie mit einem Host-Prozessor verbunden werden. Diese Lösung soll im Fiskaljahr 2018 erscheinen, in Zukunft möchte Fujitsu die Deep Learning Units zur CPU auf das Package setzen. Gleiches hat auch Intel mit den Knights Crest genannten ASICs vor.

Parallel zu den DLUs arbeitet Fujitsu am Post-K, dem Nachfolger des K-Computers. Das neue System nutzt selbst entwickelte ARM-Prozessoren mit den Scalable Vector Extensions für doppelte (FP64), einfache (FP32) sowie halbe Genauigkeit (FP16) und verwendet 512 Bit breite SIMDs.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed