Skylake-SP: Intels Xeon nutzen ein Mesh statt Ringbusse

Höhere Datentransferrate und niedrigere Latenzen: Durch eine Mesh-Topologie will Intel sicherstellen, dass die Skylake-SP-Xeons trotz noch mehr Prozessorkernen effizient rechnen. Zwei veröffentlichte Die-Shots lassen zusätzliche Details erkennen.

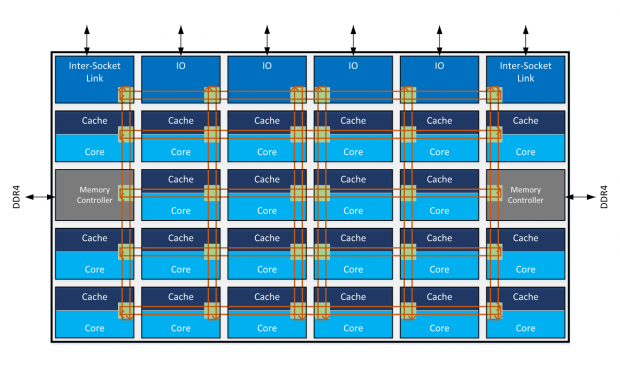

Intels kommende Xeon-Familie, intern als Skylake Scalable Processor (SKL-SP) bezeichnet, unterscheiden sich in ihrem Aufbau deutlich von bisherigen Generationen. Die Änderungen betreffen die Prozessorkerne, die privaten L2-Caches, die Blöcke der gemeinsamen L3-Zwischenpufferstufe, deren Kommunikation untereinander, die Verknüpfung von I/O-Bereichen wie dem Speichercontroller und die Verbindungen zwischen mehreren Sockeln. Möglich wird dies durch einen Mesh-Interconnect - ähnlich wie bei den aktuellen Xeon Phi alias Knights Landing genannten Prozessoren.

Seit 2010 sind bei Intels Server-CPUs die L3-Cache-Blöcke der einzelnen Kerne mit einem Ringbus verbunden. Der arbeitet bidirektional mit 32 Byte pro Takt und sorgt durch hohe Bandbreite und geringe Latenz für eine schnelle Kommunikation, was wichtig für Effizienz und Leistung ist. Von der damaligen Beckton-Generation alias Nehalem-EX bis zur heutigen Broadwell-EP/-EX-Familie hat sich die Anzahl der Kerne aber stark erhöht - von 8 auf 24.

Die Ringbus-Architektur ist ausgereizt

Daher musste Intel zwei Ringbusse verbauen, die über einen dritten Ring (ab Ivy Bridge-EP/-EX, 15C) oder vier samt Brücke (ab Haswell-EP/EX, 18C) verbunden sind. Allein diese Verbindung erhöht die Latenz um vier Taktzyklen - zusätzlich zu der, die von Kern zu Kern anfällt. Da der PCIe-Komplex und die QPI-Links für Multi-Sockel-Systeme nur an einem der Busse hängen, war abzusehen, dass Intel wie bei den Xeon Phi auf einen Mesh-Interconnect wechselt.

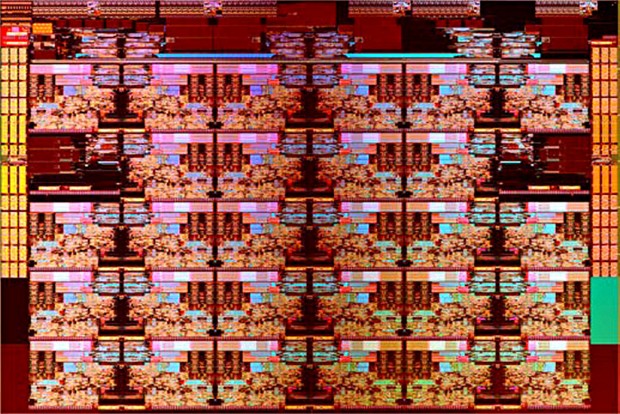

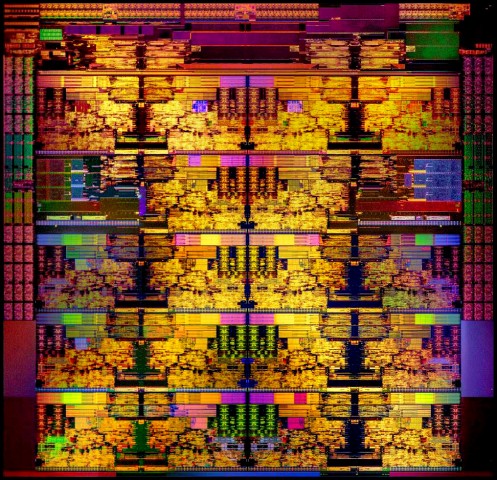

Bei Skylake-SP sind die Kerne in einem Mesh angeordnet, was zu einer höheren Datentransferrate und niedrigeren Latenzen führt, was schlussendlich in einer gesteigerten Effizienz sowie mehr Leistung resultieren soll. Intel hat bisher zwei Die-Shots veröffentlicht: einen mit 18 Kernen (High Core Count, HCC) und einen mit 28 Kernen (Extreme Core Count, XCC). Der dritte Chip dürfte angesichts von Skylake-X daher 10 Kerne aufweisen (Ligh Core Count, LCC).

6x DDR4 plus PCIe plus Interconnect

Kombiniert mit einem von Intel auf dem Server-Workshop in Hillsboro zur Verfügung gestellten, vereinfachten Blockdiagramm sind einige Details erkennbar: Das HCC- und das XCC-Die weisen zwei Speichercontroller mit je drei Kanälen auf. Oberhalb der 18 und der 28 Kerne sind 4 sowie 6 Blöcke zu sehen, dabei handelt es sich laut Hersteller um multiple PCIe-Controller und das Interface (bisher QPI), um mehrere CPUs zu koppeln. Das XCC-Die könnte also mehr PCIe-Lanes oder mehr Sockel-Interconnects nutzen.

Interessant zu wissen wäre, wie viele Taktzyklen ein einzelner Hop benötigt. Angesichts des gezeigten Aufbaus ist es ziemlich wahrscheinlich, dass ein vertikaler und ein horizontaler Hüpfer nicht die gleiche Anzahl an Takten benötigen - vor allem mit Blick auf die regulären Kerne und die Spezialknoten.

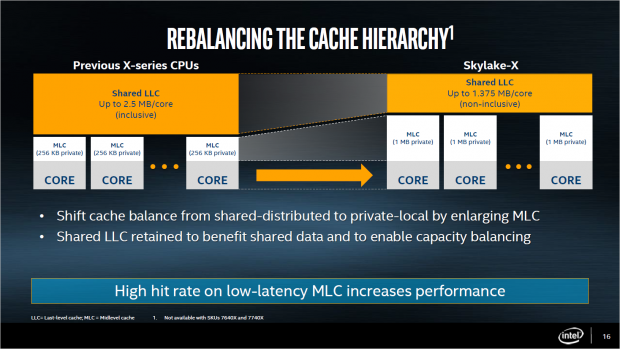

Abseits der Mesh-Architektur unterscheidet sich Skylake-SP von vorherigen Generationen auch durch seine Caches: Die zweite Stufe fasst 1.024 KByte statt zuvor 256 KByte, der dritte Puffer hingegen nur noch 1,375 MByte anstelle der bisherigen 2,5 MByte. Damit einher geht ein nicht inklusives Design, allerdings kein voll exklusives. Intel erhofft sich durch diese Änderung eine höhere Leistung, da weniger Cache-Misses auftreten dürften.

Weitere Neuerungen sind unter anderem AVX-512-Berechnungen.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

Wir haben mit unserer Software bessere Erfahrungen auf KNL als auf KNC gemacht. Man...