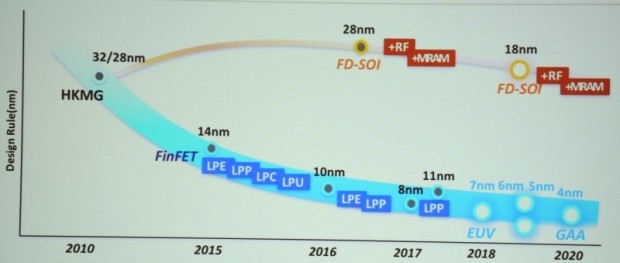

Auftragsfertiger: Samsung erweitert Roadmap bis 4 nm plus EUV

Sechs neue Herstellungstechniken: Samsung wird künftig FinFET-Verfahren von 8 nm bis hinab zu 4 nm für Prozessoren anbieten, ab 7 nm zudem mit extrem ultravioletter Strahlung. Hinzu kommt ein Node mit Sperrschicht für unter anderem MRAM.

Der Auftragsfertiger Samsung hat einen umfassenden Ausblick auf kommende Herstellungsverfahren von Mikrochips gegeben. Der Hersteller legte auf dem hauseigenen Samsung Foundry Forum im kalifornischen San Jose eine Roadmap für kommende Fertigungsprozesse, sogenannte Nodes, vor.

Aktuell bietet Samsung mehrere 14- und 10-nm-FinFet-Varianten sowie den 28FDS (FD-Soi) an. In den nächsten Monaten und Jahren möchte der Hersteller folgende neue Prozesse zur Verfügung stellen: 8LPP, 7LPP mit EUV, 6LPP mit EUV, 5LPP mit MBCFET und 18FDS. Die Nodes bauen teilweise aufeinander auf und stellen optimierte Ableger dar, wenngleich ihre Bezeichnungen etwas anderes suggerieren. Dieses Vorgehen ist bei allen Fertigern gleich.

Ab 7LPP wird EUV genutzt

8LPP (Low Power Plus) basiert auf dem bisherigen 10LPP-Verfahren, soll aber Vorteile bei der Gate-Dichte und der Taktbarkeit der Transistoren aufweisen. 7LPP ist der erste Node, der EUV-Lithografie (Extreme Ultra Violet) mit extrem ultravioletter Strahlung anstelle der bisherigen Immersionslithografie nutzt. Eingesetzt werden 250-Watt-Maschinen des niederländischen Ausrüsters ASML. 6LPP ist eine verbesserte Variante von 7LPP mit Fokus auf eine geringere Chipfläche und verringerte Leckströme.

Mit 5LPP plant Samsung laut eigener Aussage, mehrere nicht benannte technische Innovationen zu integrieren, welche die Skalierbarkeit von FinFet-Transistoren verbessern sollen. Das Ziel ist unter anderem eine reduzierte Leistungsaufnahme. 4LPP wird eine MBCFET-Struktur (Multi Bridge Channel Fet) verwenden, so nennt Samsung seine Umsetzung von GAAFET (Gate All Around Fet). Denkbar sind hier vier statt zwei Gates pro Transistor per Nanosheets.

FD-SOI auch bei Samsung wichtig

Für Hochfrequenz-Plattformen (RF, Radio Frequency) oder EMRAM (Embedded Magnetic Random Access Memory) plant Samsung das 18FDS-Verfahren. Es folgt auf den 28FDS-Prozess, basiert auf einem 14-nm-Backend und nutzt eine isolierende Sperrschicht aus Siliziumoxid (FD-SOI). Diese verhindert ein Abwandern von Elektronen, die Leckströme sinken. 18FDS ist ein Node, der für PPA (Power/Performance/Area) optimiert ist - also primär für eine niedrige Leistungsaufnahme, gefolgt von einer hohen Schaltgeschwindigkeit und einer geringen Chipfläche.

Zu welchem Zeitpunkt die neuen Nodes jeweils für die Fertigung von Chips verfügbar sein sollen, hat Samsung nicht gesagt.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

Ich widerspreche meinem Vorredner, dass ist so nicht korrekt. Die Auflösungsgrenze des...