Machine Learning: Google gibt einen tieferen Einblick in seine TPUs

Die von Google selbst entwickelten Machine-Learning-Chips, die Tensor Processing Units, sollen weitaus flotter und obendrein effizienter rechnen als Grafikkarten oder Prozessoren. Spannend ist dabei der interne Aufbau der ASICs.

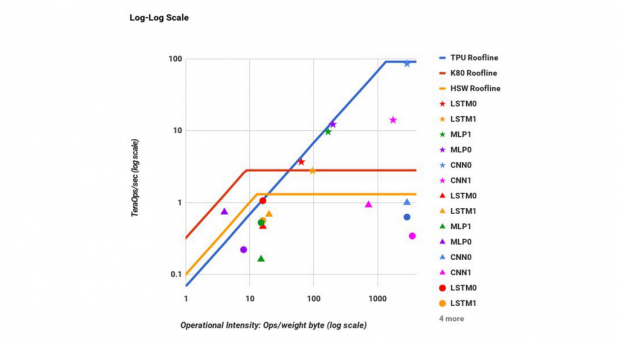

Google hat in einem Blog-Post eine Analyse verlinkt (PDF), die viele neue Informationen über die eigenen Tensor Processing Units verrät. Die TPUs sind Googles selbst entwickelte Chips für Machine Learning, die seit nunmehr zwei Jahren genutzt werden. Laut Hersteller sind die Chips um den Faktor 15 bis 30 leistungsfähiger als Prozessoren oder GPU-basierte Rechenbeschleuniger und um den Faktor 30 bis 80 effizienter, wie Messwerte belegen sollen.

Bei den Tensor Processing Units handelt es sich um ASICs, also fest verdrahtete Spezialchips. Hergestellt werden sie in einem 28-nm-Verfahren, die nominelle TDP beträgt 75 Watt bei 700 MHz - im Betrieb hat Google allerdings nur 40 Watt gemessen. Für die Leistungsvergleiche wurde ein Server mit vier TPUs gegen ein System mit zwei Xeon E5-2699 v3 (Haswell-EP) und eines mit zusätzlich vier Tesla K80 gestellt. Beide Generationen repräsentieren zwar nicht den aktuellen Stand von Intel und Nvidia, die TPUs sind aber auch schon älter.

Ein Blick auf das Blockdiagramm des ASICs zeigt, dass die eigentlichen Recheneinheiten unterrepräsentiert sind, stattdessen wird viel Platz im Chip dazu genutzt, via breiten Bussen sehr schnell Daten zuzuführen. Laut Google ist eine TDU weniger als halb so groß wie ein Haswell-EP, was unter 330 mm² bedeuten würde. Der Chip ist nicht für das Training von neuronalen Netzen gedacht, was von GPUs erledigt wird. Stattdessen hat ihn Google für Inferencing ausgelegt, er beschleunigt also ein für einen bestimmten Zweck angelerntes Netz, um etwa spezifische Details eines eingelesenen Bildes zu erkennen.

Hierfür reicht oft die Addition oder Multiplikation von Ganzzahlen, weshalb Google von TOPS (Tera Operations per Second) spricht und die TPUs einzig INT8, aber kein FP16 beherrschen. Die eigentliche Recheneinheit besteht aus rund 64.000 MACs, was rund 91,8 TOPS ergibt. Hinzu kommen ein 24 MByte großer Cache, ein DDR3-Interface mit 30 GByte pro Sekunde, ein PCIe-Gen3-x16-Anschluss und interne Leitungen, die satte 256 Byte breit sind.

Angesprochen werden die TPUs über einen CISC-Befehlssatz, der auf Googles Tensorflow-Framework angepasst ist. Ideen für die Zukunft gibt es bereits: Mit GDDR5- statt DDR3-Speicher würde die Effizienz der ASICs um den Faktor 5 steigen, mehr ASIC-Takt hingegen bringt mit DDR3 nichts.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

Nicht mal Ansatzweise so dämlich wie dein Kommentar. Clickbait? Wo? Im Artikel wird...

kwt