EMIB: Intel verbindet Multi-Chip-Module mit Silizium

Multi-Chip-Module kennt jeder Prozessorinteressierte, EMIB noch nicht. Es ist Intels Technik, um mehrere Dies mit verschiedenen Strukturbreiten zu verbinden. Das ergibt eine Art Bus, der mehrere Hundert GByte pro Sekunde schnell sein soll.

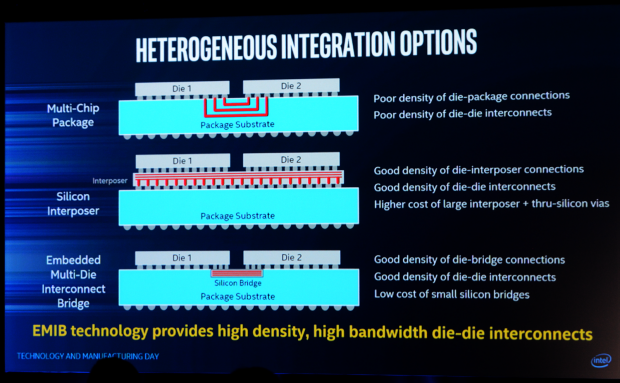

Seiner neuen Doktrin des Hyperscale folgend wird Intel auch ältere Strukturbreiten länger für neue Produkte nutzen. Dafür braucht es eine Möglichkeit, mehrere Dies in einem Chipgehäuse schnell zu verbinden. Solche Multi-Chip-Module (MCM) bieten viele Hersteller schon länger an, sie haben aber Nachteile: Entweder sind die Dies sehr schnell und damit teuer verbunden oder langsam und günstig. Die teure Variante sieht unter anderem vor, die einzelnen Dies mit vollständig durch das Silizium geführten Durchkontaktierungen (TSV) über einen großen Silizium-Interposer zu verbinden. Und viel Silizium kostet viel Geld.

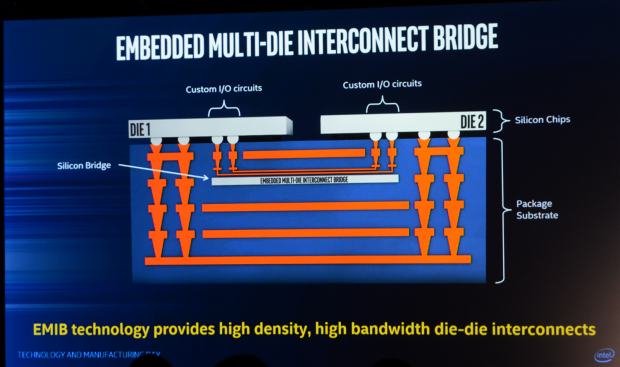

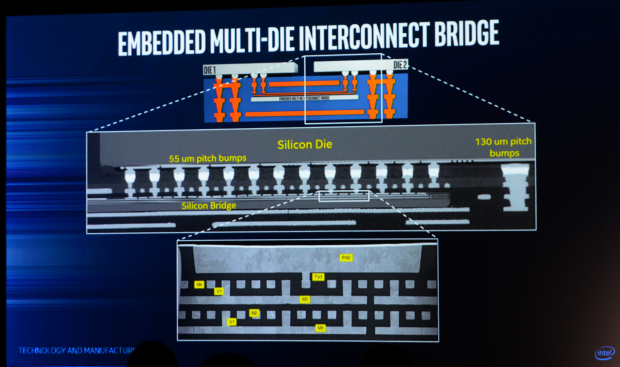

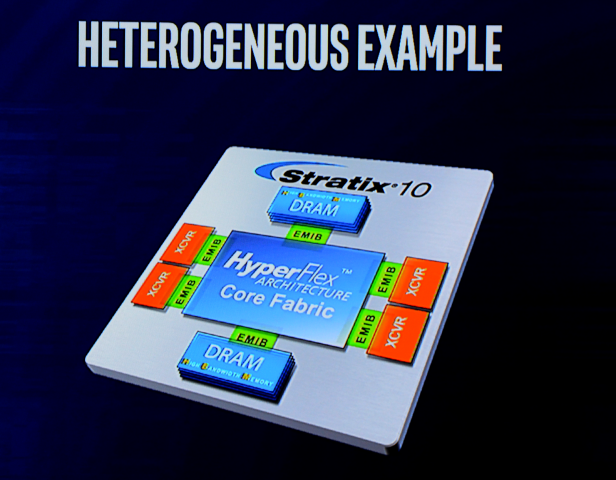

Dafür ist der Halbleiter für einen Chiphersteller auch direkt in der eigenen Fab herstellbar - er muss nur klein sein. Deshalb hat sich Intel das EMIB überlegt, die 'Embedded Multi Die Interconnect Bridge'. Dabei wird nur ein Teil der Kontaktpunkte (Bumps) des Dies über TSVs mit einem eigenen Siliziumteil im Interposer verbunden. Dafür eignen sich alle Busse - wie der zum DRAM - eines Prozessors. Sie werden ohnehin am Rand des Dies gefertigt, die Position für EMIB zu optimieren, ist laut Intel kein großer Designaufwand. Das Ergebnis soll sowohl schnell als auch kostengünstig sein. Falls das bekannt klingt: Ja, ein solches Produkt gibt es mit dem FPGA-Beschleuniger Stratix 10 schon. Dort sind aber nur die analogen Transceiver (XCVR) und die HBM2-Stapelspeicher per EMIB angebunden.

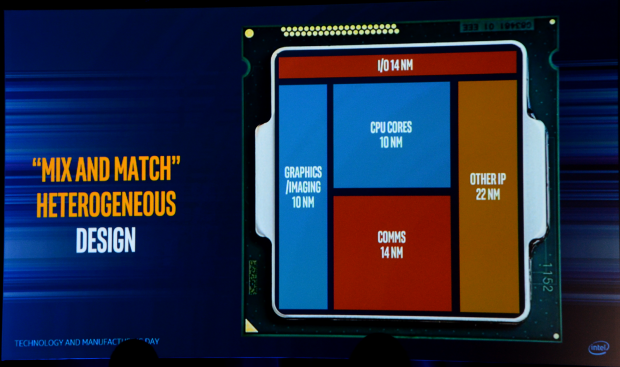

In Zukunft, so sagte Intel auf seinem Manufacturing Day in San Francisco, könnten auch viele Teile einer PC-CPU durch EMIB verbunden werden. Die schnellsten x86-Cores könnten in 10-nm-Technik gefertigt werden, die Schnittstellen in 14 Nanometer, eine GPU mit anderen Anforderungen an die Transistoren auf einem weiteren 10-nm-Die und Spezialfunktionen wie FPGA-Beschleuniger mit 22 Nanometern. Das gezeigte Bild stellt zwar noch ein fiktives Konzept dar, es soll aber technisch machbar sein. Schon länger gibt es Gerüchte, dass Intel für das auf dem Bild 'Other IP' genannte Design vielleicht auch einmal eine AMD-GPU lizenzieren könnte - oder das gar nicht muss, weil Intel und AMD schon seit Jahrzehnten ein Patentaustauschabkommen unterhalten.

Zur Leistung der EMIB-Verbindung machte Intel keine genauen Angaben, nur von "einigen Hundert GByte pro Sekunde" war die Rede. Das ist die Größenordnung, die heute nur die kurzen Verbindungen von GPU zu GDDR5-Speicher auf einer Grafikkarte erreichen, noch kürzere Verbindungen wie in HBM2-Stapeln sind noch fixer. Ebenso wollte Intel auch auf Nachfragen nicht angeben, ob EMIB auch für mehrere Dies mit x86-Kernen in einem Chipgehäuse dienen soll. Das gab es sowohl bei Intel als auch bei AMD schon öfter, beide Unternehmen wurden von Technikfans für 'zusammengeklebte' Dies verspottet. EMIB ist nach den bisherigen Angaben aber so schnell, dass sich auch bei Mehrkern-Dies nur geringe Geschwindigkeitsnachteile ergeben dürften.

Denkbar sind dennoch neben der Flexibilität der Bestandteile eines Chips auch Kostensenkungen bei Intel selbst, wenn etwa mehrere Xeon-Dies mit teils nicht funktionierenden Kernen gekoppelt werden - das erhöht die nutzbare Ausbeute in der Fertigung. Bestätigen wollte Intels Client- und IoT-Chef Dr. Murthy Renduchintala das jedoch nicht. Auf die konkrete Frage nach EMIB-Xeons antwortete er nur mit der höflicheren Kein-Kommentar-Alternative: "Das ist eine sehr gute Idee."

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

Ich meinte eher, dass man direkt die Chipfläche so verkleinert, dass weniger Kerne auf...