Moore's Law: Hyperscaling soll jedes Jahr neue Intel-CPUs sichern

Tick Tock ist tot, Moores Law aber ganz und gar nicht: Intel will weiter jährlich neue Prozessorgenerationen vorstellen, die eigentlichen Strukturbreiten aber nicht regelmäßig verkleinern. Der Kniff dafür heißt Hyperscaling.

Zum Start des ersten Manufacturing Day seit drei Jahren hat Intels Chef der Fertigungsabteilung, Stacy Smith, eine neue Maßeinheit für die Chipherstellung eingeführt: Hyperscaling. Das ist ein Marketingbegriff, der unterstreichen soll, dass Intel die Verkleinerung der Chipstrukturen alle zwei Jahre - wie es Moore's Law vorschreibt - für wirtschaftlichen Erfolg nicht braucht.

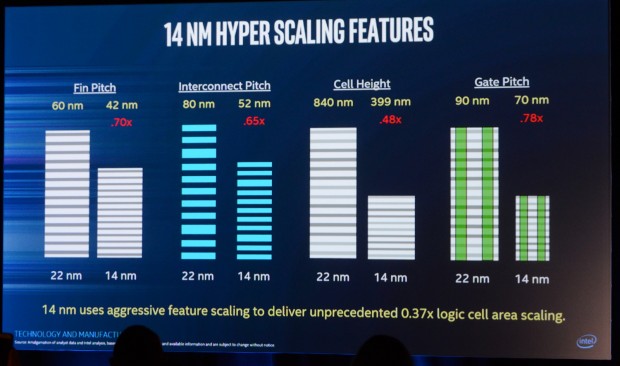

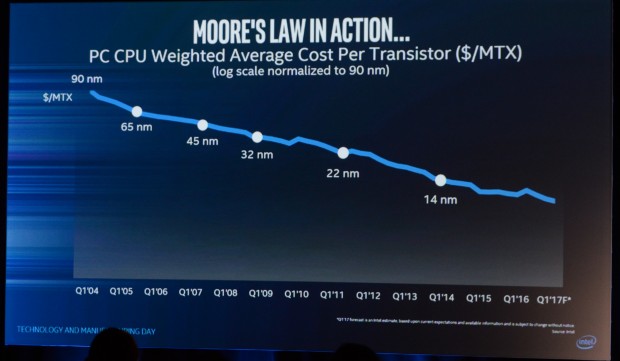

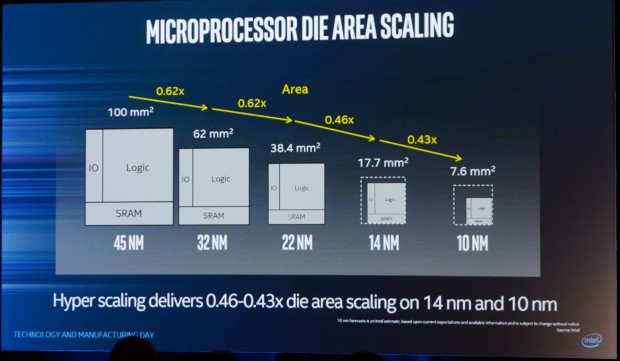

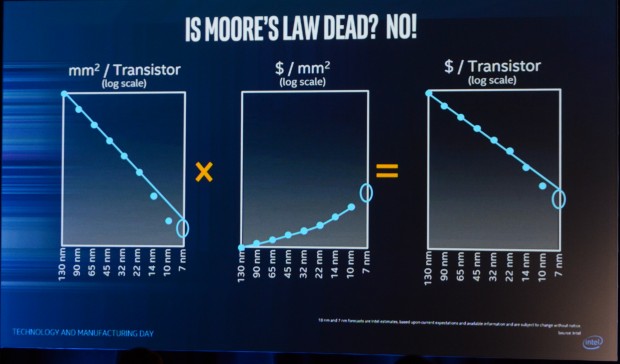

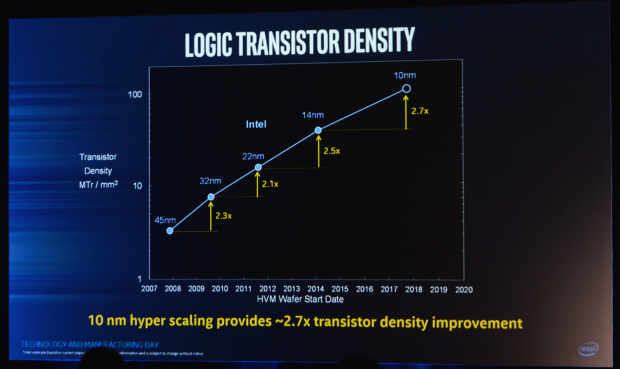

Dass die vom Intel-Mitbegründer Gordon Moore formulierte Regel tot sei, wie viele Analysten und Intel-Konkurrenten seit Jahren behaupten, wies Smith von sich. Er gab zwar zu, dass sich die Zeit von einem Node, wie aktuell dem Wechsel von 14 zu 10 Nanometern Strukturbreite, zum nächsten verlängere. Dafür sänken die Kosten pro Transistor aber von einem Node zum nächsten inzwischen stärker als das früher der Fall gewesen sei. Technisch wichtiger: Durch Optimierung der aktuellen Strukturbreite lassen sich auch ohne einen neuen Node mehr Transistoren auf gleicher Fläche herstellen.

So ist aktuell Kaby Lake (7th Gen) schon die dritte CPU-Generation mit 14-nm-Technik. Die Kosten der Herstellung pro Transistor sind von Broadwell über Skylake bis Kaby Lake stetig gesunken. Ebenso passen mehr Schalteinheiten auf die gleiche Fläche. Das hat Smith zufolge einen ähnlichen Effekt wie eine Verkleinerung, also dem nächsten Node, denn: Das Ziel ist stets, mehr Funktionen eines Chips bei gleichen oder geringeren Kosten zu erreichen. Das können unter anderem mehr Kerne, größere Caches oder bessere Grafikeinheiten sein.

Vor allem auf Letztere legte Intel in den vergangenen Jahren bei Desktop- und Notebook-CPUs den größten Wert, die Leistung pro Takt (IPC) erhöhte sich immer nur wenig. Mit der durch Ryzen erstarkten Konkurrenz von AMD dürfte sich das wieder ändern. Die neue Metrik des Hyperscaling bedeutet darüber hinaus nicht, dass Intel die 10-Nanometer-Technik verschiebt, sie steht weiterhin für das 2018 erwartete Design Cannon Lake an.

Nachtrag vom 28. März 2017, 23:59 Uhr

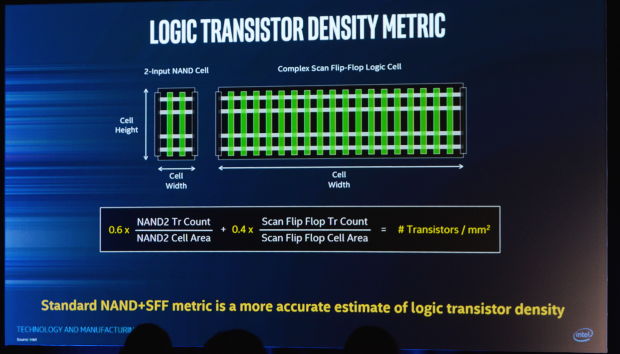

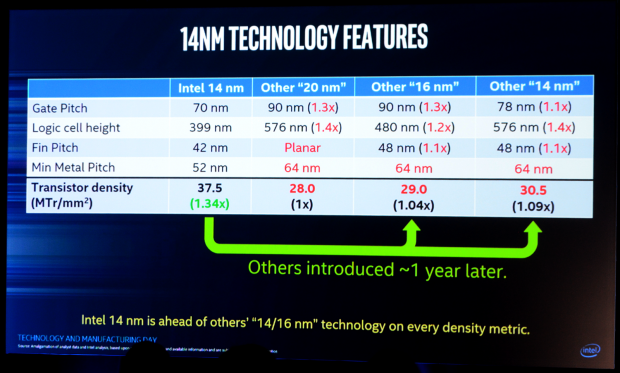

Nach Smiths Präsentation erklärten Intels Fertigungsexperte Mark Bohr und zwei seiner Kollegen, wie Intel sich einen fairen Vergleich von Strukturbreiten vorstelle - ohne die klassischen Nodes, sondern anhand der Packdichte der Transistoren. Während bei allen Konkurrenten - grob vereinfacht - der Abstand der Transistoren jeweils aktuell zwischen 20 und 14 Nanometern liegt, sind Intels Schaltelemente viel kleiner.

Bohr schlug vor, die Zahl der Transistoren pro Quadratmillimeter über den gesamten Chip heranzuziehen. Dafür legte er eine Formel vor, die sich an NAND-Strukturen - wie bei Flash-Speicher - orientiert. Zwar können andere Elemente wie I/O-Schaltungen oder Caches andere Größen erreichen, die NAND-Dichte biete sich aber an, weil sie gleichförmig sei, sagte der Intel-Fellow. Daran gemessen bringt Intels 14-Nanometer-Prozess für CPUs rund 30 Prozent mehr Transistoren pro Quadratmillimeter als bei den Mitbewerbern unter. Auch bei anderen Kenngrößen wie den Abständen der Leiterbahnen, der minimalen Entfernung der Durchkontaktierungen (Vias), sind die Intel-Chips effizienter.

Beim genauen Vergleich ist das lange bekannt, in der Halbleiterbranche hören wir häufig Aussagen wie: "Was bei Intel 22 Nanometer sind, schaffen die anderen nur mit 14." Neu ist aber, dass Intel sich klar dazu bekennt, seltener neue Nodes einzuführen und seinen Vorteil bei der Packdichte als Teil von Moore's Law verstanden wissen will. Das soll auch in Zukunft so bleiben, jeder Node wird in zwei Stufen weiterentwickelt. Nach 14nm folgt 14nm+, dann 14nm++. Auch bei 10 Nanometern soll das so bleiben. Etwa alle drei Jahre, nicht mehr alle zwei, erfolgt also eine Verkleinerung der Basisstrukturbreite.

Wie bereits berichtet ist diese Verlagerung auf Optimierungen vor allem der Kosteneffizienz geschuldet, auch als Moore's 2nd Law bekannt. Inzwischen ist Stacy Smith zufolge der Bau einer Chipfabrik für eine neue Strukturbreite mit zehn Milliarden US-Dollar so teuer geworden, dass die Anlagen eine wesentlich längere Laufzeit erreichen müssen als noch vor einigen Jahren.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

Ein paar kleine Anmerkungen: Der Q9550 hat damals ¤250 und der i7-6700k ¤350 gekostet...

Habe ich entfernt. Nie gebraucht.

Wer sagt es Murphy?

Wieso? DCTs macht z.B. jeder JPEG Encoder en masse ;-)