Prozessor: Ryzen benötigt weniger Fläche als Intels Kaby Lake

Obgleich Intel die bessere Fertigungstechnik nutzt, hat AMD seine Ryzen-CPUs so designt, dass sie trotz teils mehr Cache schlanker ausfallen als Kaby Lake. Das könnte zwar mit Nachteilen einhergehen, verringert aber die Kosten.

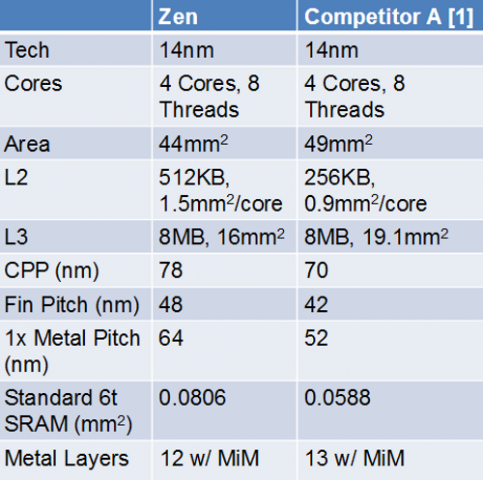

AMD hat auf der International Solid State Circuits Conference 2017 (ISSCC) neue Informationen zu seinen Ryzen-CPUs bekanntgegeben, wie die EE Times berichtet. Der Hersteller möchte verglichen mit Intel ein Quadcore-Design entwickelt haben, das nur 44 statt 49 mm² misst. Diese rund zehn Prozent sind insbesondere deswegen interessant, weil Intel das technologisch etwas fortschrittlichere Herstellungsverfahren nutzt und AMD größere Zwischenpuffer pro Kern verwendet, die dennoch dichter gepackt sind.

Konkret bezieht sich AMD auf einen CCX (CPU Complex) mit vier Zen-basierten Kernen mit SMT, von denen jeder auf 512 KByte L2-Cache zugreifen kann, und 8 MByt L3-Cache. Intel hingegen verwendet pro Kern seit vielen Jahren nur 256 KByte, so auch beim zum Vergleich herangezogenen Quadcore. AMD gibt an, für jeden der vier L2-Caches eine Fläche von 1,5 mm² zu benötigen und Intel würde für die Hälfte auf 0,9 mm² kommen. Der L3-Cache sei mit 16 statt 19,1 mm² ebenfalls kompakter.

Die restliche Die-Size entfällt auf die CPU-Kerne mit ihren L1-D/L1I-Caches. Wie groß eine komplette Ryzen-CPU mit zwei CCX ist, verrät AMD nicht. Zu den 88 mm² kommen noch diverse I/O-Teile wie PCIe-Lanes, Sata und USB hinzu, auch der Speichercontroller sowie diverse Busse benötigen weiteren Platz.

Interessant ist jedoch, dass die SRAM-Zellen, aus denen die Caches bestehen, über ein Drittel größer sind als bei Intel. Das bedeutet, dass AMD die Zwischenpuffer weitaus enger packt, was eventuell mit weniger Durchsatz, höheren Latenzen und geringerem Takt einhergehen könnte.

AMD braucht kleine Dies für hohe Margen

Generell ist es für AMD aber wichtig, dass es sich bei Ryzen um ein kompaktes Design handelt, das günstig hergestellt werden kann. Hinzu kommt, dass Ryzen mit 12 statt 13 Metall-Layern eventuell weniger aufwendig zu fertigen ist.

AMD nutzt das 14LPP-Verfahren bei Globalfoundries, das von Samsung lizenziert wurde, Intel hingegen sein eigenes 14FF+. Der Fin- wie Gate-Pitch fällt beim 14FF+ kleiner aus.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

Die Angegebene Fläche (0,0806 mm²) pro 6t SRAM Cell passt in keiner Weise zu den anderen...

Eben. Bei Intel waren voher schon 8 Pilze auf dem Die unterwegs und haben ihre Spuren...

Polaris war für 20 nm geplant.