Power9: IBMs 24-Kern-Chip kann 8 TByte RAM pro Sockel nutzen

Big Blue gegen Intel: Der Power9-Prozessor tritt gegen die Xeon E5/E7 an. Bis zu 24 Kerne mit 8-fachem SMT, Unmengen an Cache, eine moderne Fertigung und einige Zentauren sollen dabei helfen.

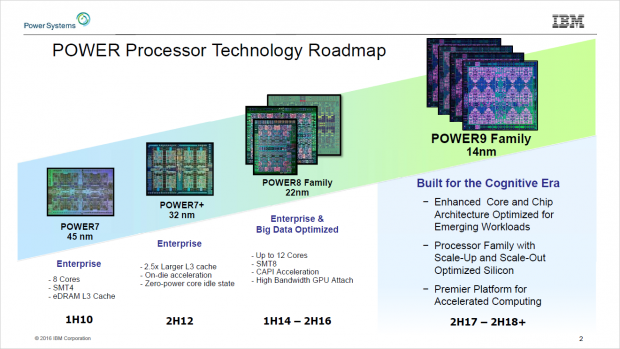

IBM hat auf der Hot Chips 28 im kalifornischen Cupertino den Power9 vorgestellt: Die Prozessorreihe umfasst vorerst vier Modelle, um unterschiedliche Märkte adressieren zu können. Generell werden die Power9 im Scale-Out-Segment mit Single- oder Dual-Sockel-Systemen gegen Intels Xeon E5 sowie für das Scale-Up-Umfeld gegen die Xeon E7 positioniert. Dafür braucht es viel Leistung - die Daten sind dementsprechend beeindruckend.

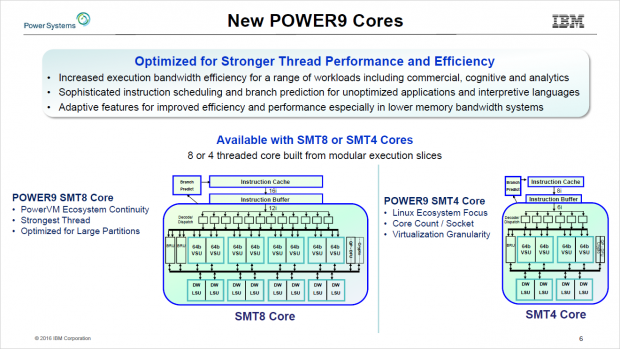

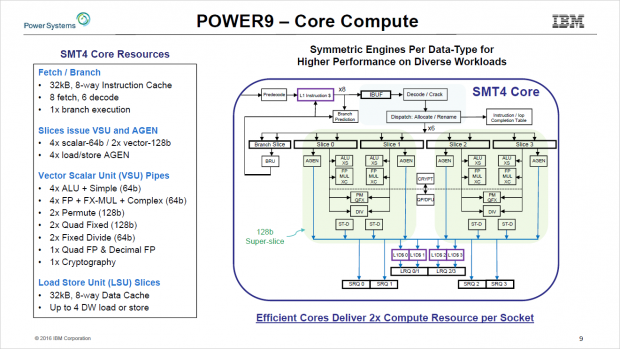

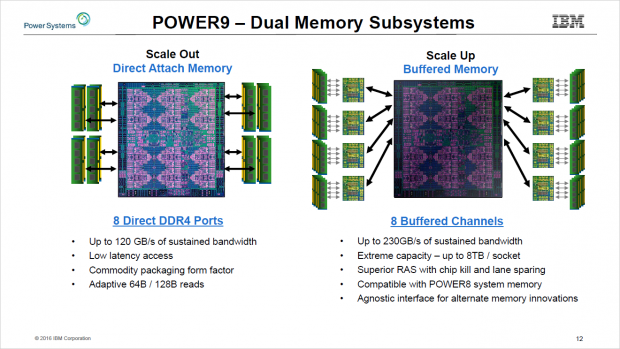

Die vier Varianten nutzen 24 oder 12 Kerne und 4-faches sowie 8-faches Simultaneous Multithreading, was IBM durch unterschiedliche Kerne realisiert: Das Front- wie das Backend sind doppelt ausgelegt, damit die Threads über die nötigen Ressourcen verfügen. Der Unterschied zwischen Scale-Out und Scale-Up besteht in der Speicherbindung: Der Power9 SO (Nimbus) hat acht DDR4-Speicherkanäle für theoretisch 4 TByte Speicher, was jedoch 256-GByte-Module voraussetzt. Die Datentransferrate soll bei bis zu 120 GByte die Sekunde liegen.

Beim Power9 SU (Cumulus) sitzen acht zusätzliche Centaur-Chips für Buffered Memory auf dem Package, von denen jeder vier statt nur zwei DDR4-2666-Sticks pro Kanal ansprechen kann - das macht 8 TByte pro Sockel. Jeder der Zentauren weist überdies 16 MByte eigenen Speicher auf, was zusammen 128 MByte L4-Cache macht, wie schon beim Power8. Durch die Centaur-Chips lädt der Power9 SU Daten mit bis zu 230 statt mit bis zu 120 GByte pro Sekunde.

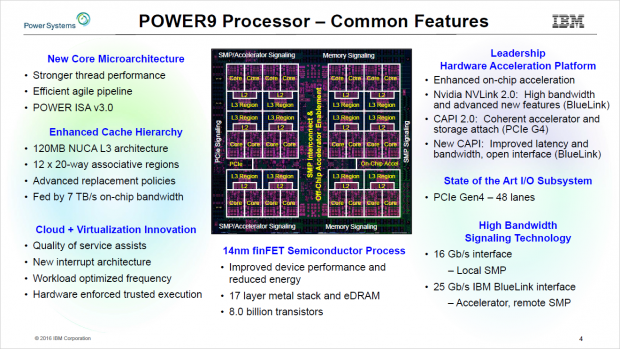

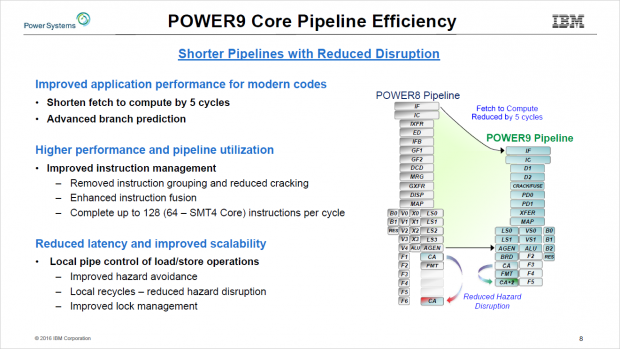

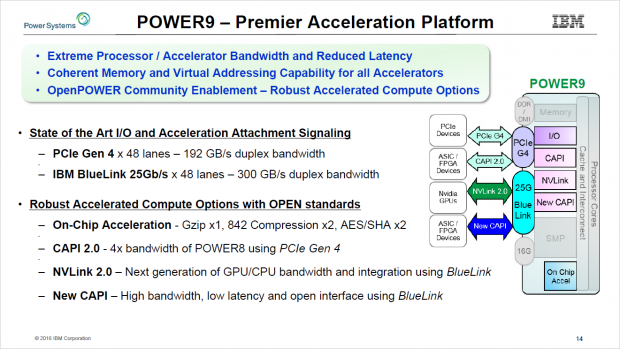

Die eigentlichen Kerne sind mit einer kürzeren Pipeline als noch beim Power8 und Power8+ versehen und arbeiten mit der neuen Power ISA v3. Jeder Kern verfügt über je 32 KByte L1-Instruktionen- und L1-Daten- sowie 512 KByte eigenen L2-Cache, hinzu kommen 120 MByte L3-Puffer für alle zusammen. Mit im Chip sitzen 48 PCIe-4.0-Lanes sowie ein Phy, über das der Bluelink (48 x 25 Gbps) angebunden ist. Das ermöglicht den Anschluss von FPGAs via New CAPI oder von Nvidias Tesla P100 per NV Link 1.0 in der Modulversion. Kommende Volta-Karten sollen NV-Link 2.0 in Kombination mit einem Power9 ermöglichen.

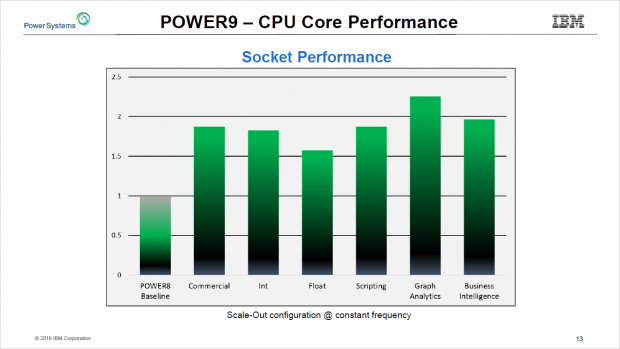

Gefertigt werden die Power9 in Globalfoundries Fab 8 in Malta, New York im 14HP-Verfahren (14 nm FinFET High Performance mit Silicon-on-Insulator, SOI). Das hatte der Auftragsfertiger samt der Fab 10 in East Fishkill, New York Ende 2014 übernommen. Der größte Power9 weist 17 Metal-Layer und 8 Milliarden Transistoren bei einer Fläche von 693 mm² auf. IBMs eigene Benchmarks sehen den Chip bei gleichem Takt (4 GHz) um den Faktor 1,6x bis 2,3x vor dem Power8.

Im zweiten Halbjahr 2017 will IBM den Power9 für Scale-Out ausliefern, ab 2018 sollen die Scale-Up-Varianten für vier und acht Sockel folgen. Die Gegner werden damit folglich Intels Skylake-EP/EX mit bis zu 28 Kernen.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

Intel bereits abgeschlagen, Zen bzw Summit Ridge mit 4 GHz - was hab ich verpasst...

Du meinst Kodierungen.