Summit Ridge: Das kann AMDs CPU-Architektur Zen

Größere Buffer sowie Caches samt Hyperthreading, skalierbar von passiv gekühlten Tablets bis hin zu Supercomputern und keine Module mehr: Die Zen-Architektur wird die Basis fast aller AMD-Prozessoren der nächsten Jahre bilden. Ein erster Überblick.

Nachdem AMD vergangene Woche auf einem 'Konter-Event' parallel zu Intels Developer Forum erste Informationen und Benchmarks zu den kommenden CPUs namens Summit Ridge (Desktop) und Naples (Server) veröffentlicht hat, folgen diese Woche weitere Informationen: Auf der Hot Chips 28, einem Chip-Symposium in Cupertino, spricht AMDs Senior Fellow Mark Clark über weitere Details der zugrundeliegenden Zen-Mikroarchitektur.

Vorneweg sei gesagt, dass allen Teilnehmern der Hot Chips die Präsentation vorliegt. Wir werden uns diese Woche vor Ort mit Mark Clark unterhalten und diese Meldung gegebenenfalls mit weiteren Einzelheiten aktualisieren - darunter fallen Fragen zur Kommunikation der Cluster, des Speichersubsystems, der erreichbaren Taktraten und Besonderheiten der Caches. Grundsätzlich sei gesagt, dass die auf dem Chip-Symposium erläuterten Details das bestätigen, was die Linux-Kernel-Patches zeigen und teils mehr Tiefe liefern.

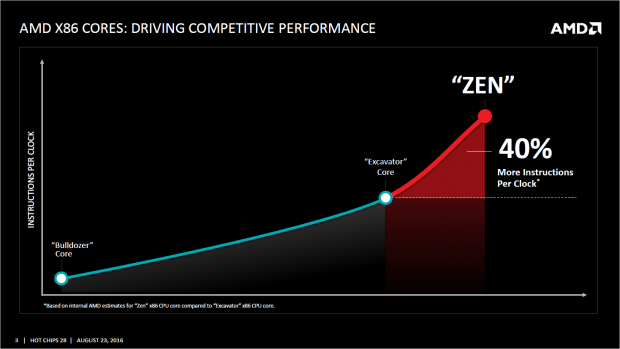

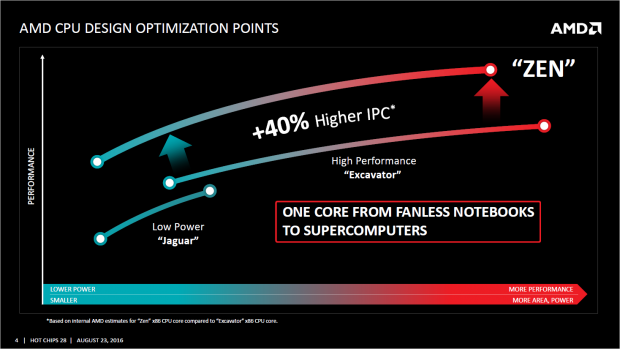

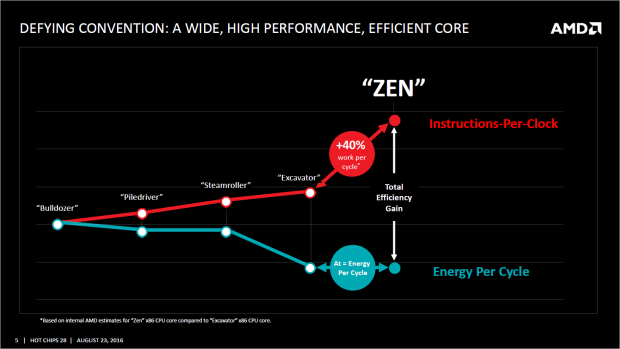

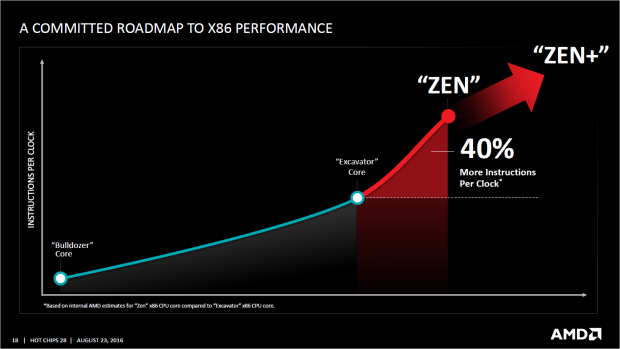

Anders als die Bulldozer-Technik, die auf Module mit hoher Integer-Leistung und eine Gleitkomma-Einheit mit Fokus auf Befehlssatzerweiterungen wie AVX/FMA aufweist, handelt es sich bei der Zen-Architektur um einen klassischen Ansatz, der mit 'Wald- und Wiesen-Code' weitaus bessere Resultate erzielen dürfte. AMD spricht von +40 Prozent mehr Leistung pro Takt verglichen mit Excavator und von über 3 GHz für die schnellsten Desktop-Modelle mit acht Kernen.

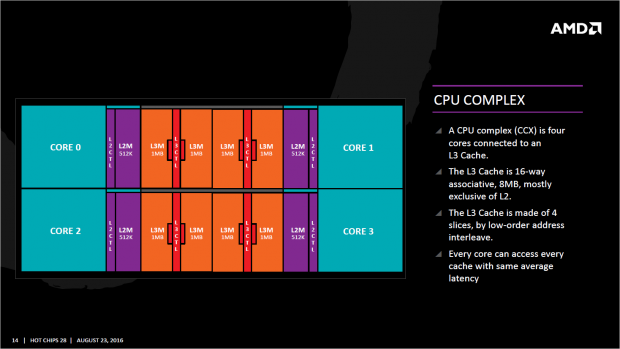

Die Zen-Kerne sollen von passiv gekühlten Notebooks - also wohl Detachables - bis hin zu Supercomputern skalierbar sein. Das würde eine angebliche Roadmap bestätigen: Die spricht von 4,5 bis 95 Watt - Naples (32 Kerne) für Server sind hier allerdings außen vor. Die Grundlage aller Designs bildet ein CCX (CPU Complex), so nennt AMD einen Block aus vier Kernen samt 8 MByte L3-Cache. Zwei davon werden für Summit Ridge verwendet.

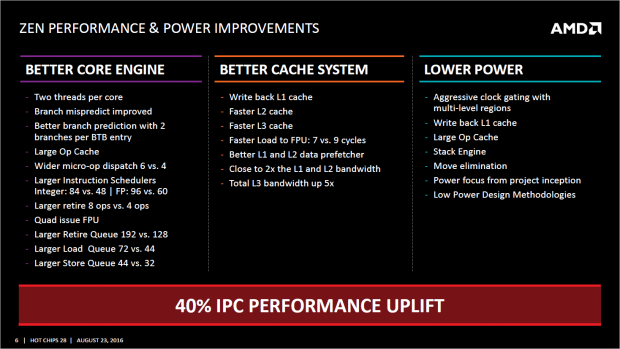

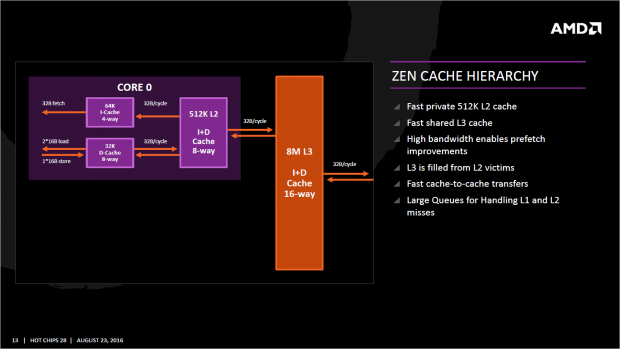

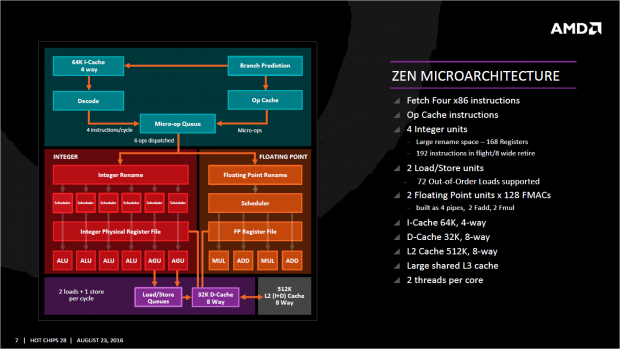

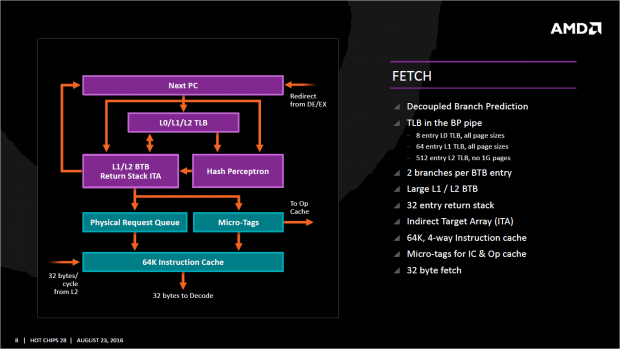

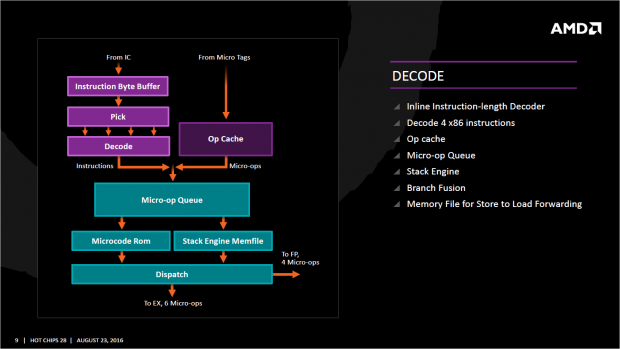

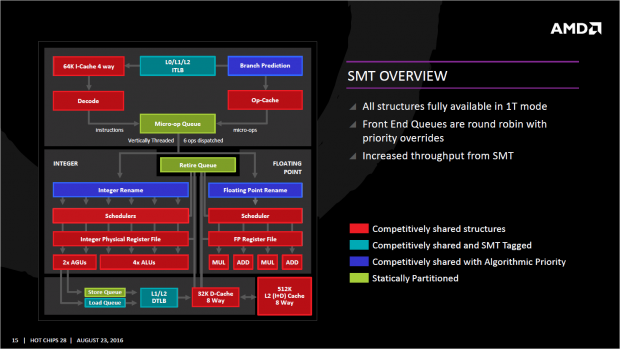

Beginnen wir klassisch beim Frontend: Die Sprungvorhersage wurde wie üblich verbessert und puffert ihre Daten in den 4-fach statt 2-fach assoziativen (weniger Cache Misses!) L1-Instruktionen-Cache mit 64 KByte oder den neuen Micro-Op-Cache. Den kennen wir von Intels Sandy Bridge, unklar bleibt aber das Fassungsvermögen - ungeachtet werden so die Recheneinheiten besser ausgelastet und die Effizienz steigt. Pro Takt kann Zen vier Instruktionen decodieren und dann immer sechs µOps an das Backend verteilen (Floating Point oder Integer oder beides gleichzeitig für eine bessere Auslastung).

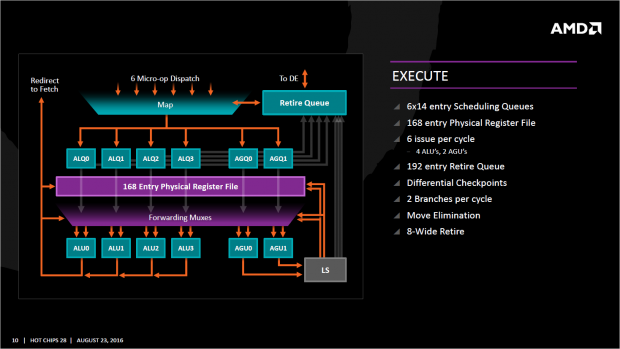

AMD nutzt anders als Intel eigene Scheduler für die Float- und Integer-Einheiten, was für mehr Durchsatz sorgt. Mit zwei Ports für Load/Store sowie je vier für FP und INT ist Zen breiter aufgestellt als Intels aktueller Skylake-Kern, was für SMT hilfreich sein sollte. Passend hat AMD quasi alle Buffer verglichen mit Excavator aufgebohrt, in den meisten Fällen (Scheduler, Load/Store-Queue, OoO-Fenster) liegt deren Kapazität zwischen Haswell und Skylake - da wundert es wenig, dass Zen in etwa auf dem Level von Intels Broadwell liegen soll.

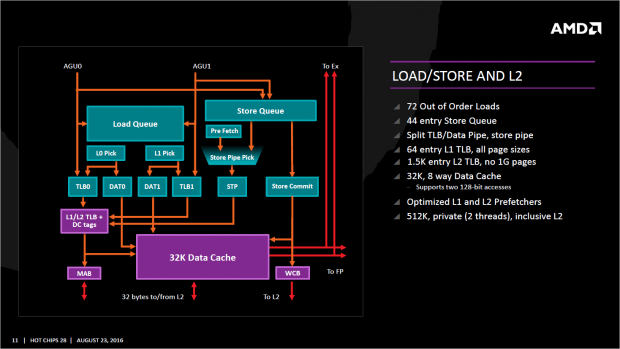

Der Integer-Block besteht aus vier ALUs und zwei AGUs, wobei Letztere den nun 8-fach assoziativen und 32 KByte fassenden L1-Daten-Cache nutzen, der als schneller Write-Back- statt wie bisher als langsamerer Write-Through-Puffer konzipiert ist. Wie der L1I soll auch der L1D sehr latenzarm arbeiten, was AMD auch vom L2 behauptet. Der ist 8-fach assoziativ angebunden und 512 KByte groß, was beides eine Verdopplung verglichen mit Skylake bedeutet. Einige L2-Daten landen im exklusivem L3-(Victim-)Cache, der 8 MByte pro Quadcore fasst und mit Kerntakt läuft. Der Puffer ist in acht Blöcken organisiert, einen Last Level Cache für alle acht Kerne gibt es ergo nicht.

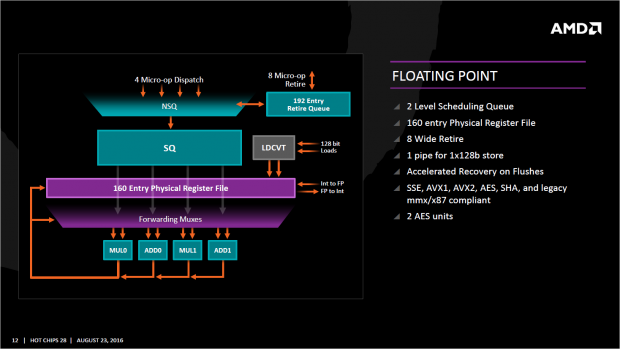

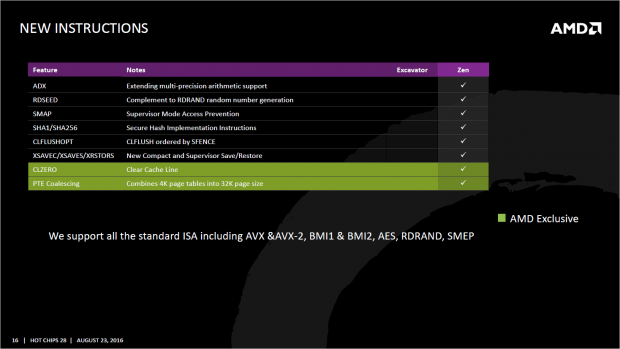

Die vier stärker parallelisierten Float-Ausführungseinheiten beherrschen AVX und AVX2, wobei Letzteres anders als bei Intel in zwei Zyklen (sogenannte Doubles) abgearbeitet werden muss. Für Consumer-Software spielt das vorerst keine Rolle. Ebenfalls unterstützt wird eine AES-Verschlüsselung, neu sind unter anderem RDSEED und SHA1/SHA256 sowie zwei AMD-exklusive Instruktionen. Anders als die bei Bulldozer pro Modul aufgeteilte FP-Einheit soll die neue bei einem Flush viel flotter wieder ihre Arbeit aufnehmen.

Um den Durchsatz zu steigern, kann jeder Zen-Kern per SMT zwei Threads abarbeiten, Intel nennt das Hyperthreading. Das Frontend kann daher teilweise dynamisch aufgeteilt werden, das Backend verarbeitet generell Befehle aus beiden Threads. Je nach Code dürfte durch SMT die Leistung grob um 15 bis 20 Prozent steigen; bei manchen Spielen sinkt bei Intel durch Hyperthreading die Leistung - das gilt es aber für Zen noch auszutesten.

Unterm Strich ähnelt AMDs neue Architektur an einigen Stellen aus High-Level-Sicht, sprich oberflächlich, an Intels Haswell bis Skylake, was keinesfalls negativ auszulegen ist. Das Zen-Design wurde verglichen mit Bulldozer fast durchgehend verbreitert, die Buffer und Caches entsprechend skaliert und somit die wichtige Instruction-Level-Parallelität drastisch erhöht.

Etwaige Schwachstellen dürften sich erst im Test offenbaren, zumal die Frequenzen und Leistungsaufnahme bisher einzig grob umrissen wurden. Wir können es nur wiederholen: Es wird spannend, wie hoch Summit Ridge bei welcher TDP taktet und wie abseits der Octa- die etwaigen Quadcore-Varianten aussehen. Obendrein hat sich AMD bisher offiziell weder zum Speicherinterface noch zu den PCIe-Lanes oder dem Uncore geäußert.

Bis Anfang 2017 wird sich das und mehr aber klären.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

Rosinenpicken. Rendern ist nicht Rendern. Du raffst es einfach nicht, also lass es. Und...

Deswegen schrieb ich ja mindestens ;) Du hast ja nur deine Plattform gepostet, nicht aber...

Nein, aber 8.

Wie lange ein Laptop durchhält, liegt in erster Linie am Display, nicht an der CPU.