Drive PX 2: Pascal-Chips nutzen ein 128-Bit-Interface mit GDDR5-Speicher

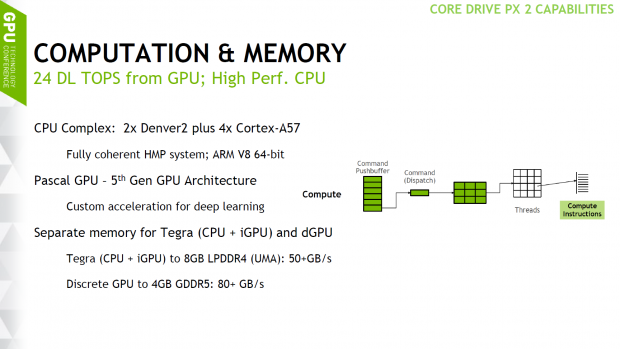

Die beiden Pascal-GPUs auf dem Drive PX 2 sind mit 128 Bit an 4 GByte GDDR5-Speicher angebunden, die Parker genannten Tegra-SoCs mit 128 Bit an 8 GByte LPDDR4. Das wirft einige Fragen auf.

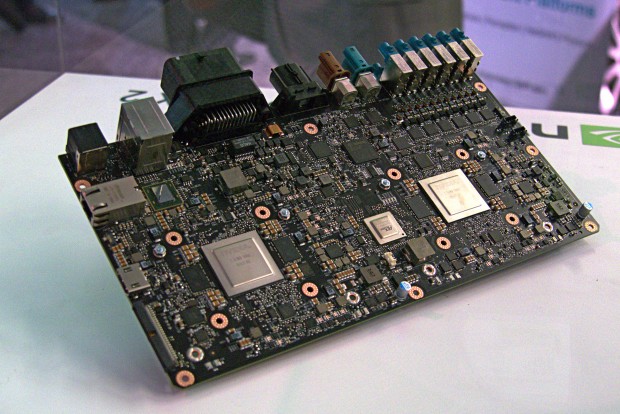

Nvidia hat auf der GDC Technology Conference 2016 in San Jose, Kalifornien, einen tieferen Einblick in die Hardware des Drive PX 2 gegeben. Das für autonome Fahrzeuge gedachte Hardwaremodul wurde auf der Consumer Electronics Show im Januar 2016 vorgestellt, damals allerdings noch mit Maxwell-basierten Grafikchips. Auf der Hausmesse hingegen zeigt Nvidia das Drive PX 2 mit anderen GPUs, bei denen es sich um Pascal-Modelle handeln dürfte. Parallel dazu sprach der Hersteller in einer Session über das Interface und den Videospeicher der Pascal- und der zusätzlichen Tegra-Chips.

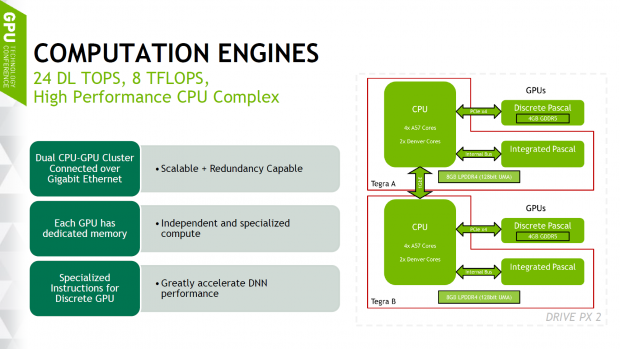

Das Drive PX 2 besteht laut Nvidia aus zwei Pascal-GPUs und zwei Tegra-SoCs mit dem Codenamen Parker. Wie vorherige Modelle basiert die Bezeichnung auf einem Superhelden, in diesem Fall Peter Parker - also Spiderman. Zusammen sollen die vier Chips eine Rechenleistung von 8 Teraflops bei einfacher Genauigkeit liefern, wobei unklar ist, wie sich der Wert zusammensetzt. Die thermische Verlustleistung des Drive PX 2 beträgt 250 Watt, weshalb das Modul mit einer vormontierten AiO-Wasserkühlung ausgeliefert wird.

In einer Präsentation sagte der Hersteller, dass die beiden Pascal-GPUs mit einer Transferrate von über 80 GByte pro Sekunde Daten aus den 4 GByte GDDR5-Videospeicher beziehen. Das bedeutetet, dass die Chips per 128-Bit-Interface angebunden sind. Ein ausgestelltes Drive PX 2 zeigt längliche GPUs, die offenbar vergangene Woche im A1-Stepping gefertigt wurden. Hinzu kommen 8 statt 4 GByte GDDR5-Videospeicher, genauer solcher von Elpida mit 3,5 GHz. Das Hardwaremodul steckt allerdings nicht in einem funktionsfähigen Fahrzeug, es könnte sich daher schlicht um ein kurzfristig gebautes Mockup handeln.

Zusammen mit der Die-Size und dem MXM legt der Aufbau nahe, dass es sich bei den verbauten Chips um GP106-Modelle handelt. Die dürften ein 128-Bit-Speicherinterface aufweisen und sind abseits des für autonome Fahrzeuge gedachten Hardwaremoduls für Notebook-Grafikeinheiten der unteren Leistungsklasse gedacht. Die Anzahl der Shader-Einheiten bleibt vorerst offen.

Beim Parker-SoC verwendet Nvidia zwei selbst entwickelte Denver-Kerne, die mit einem Custom-Interconnect mit vier Cortex-A57 verbunden sind. Das Interface liefert über 50 GByte pro Sekunde, ist also 128 Bit breit. Daran hängen 8 GByte LLPDDR4-Speicher. Zur im Tegra steckenden integrierten Grafikeinheit äußerte sich Nvidia erneut nicht. Einzig, dass sie auf der Pascal-Architektur basiert, hat der Hersteller bisher offiziell bestätigt.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed