Broadwell-EP: Intel zeigt Xeon E5 mit Arria-FPGA auf einem Package

Intel hat erstmals einen der angekündigten Xeons mit angekoppeltem FPGA von Altera gezeigt. Der 15-kernige Broadwell-EP dürfte durch einen speziellen Bus mit dem Arria-Chip verbunden sein.

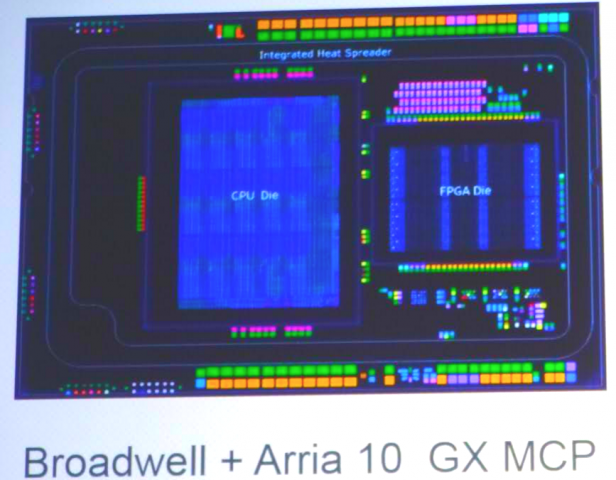

Der Prozessorhersteller Intel hat auf dem OCP Summit in San José einen Prozessor mit einem FPGA auf einem Package ausgestellt. Dem Bericht von The Next Platform zufolge handelt es sich dabei um einen Xeon E5 alias Broadwell-EP mit einem Arria 10 GX von Altera. Intel hatte den FPGA-Spezialisten im Sommer 2015 für knapp 17 Milliarden US-Dollar übernommen und im Herbst erste Prototypen-Systeme gezeigt.

Beim verwendeten Xeon handelt es sich um einen Broadwell-EP mit 15 Kernen, was dem mittleren (MCC, Medium Core Count) der drei geplanten Dies entspricht - das größte soll bis zu 24 Kerne bieten. Hergestellt werden diese Chips in Intels aktuellem 14FF-Verfahren. Der Arria-FPGA hingegen ist ein Produkt der Taiwan Semiconductor Manufacturing Company, dort erfolgt die Herstellung im planaren 20-mn-Prozess. Die bisherigen Prototypen-Systeme koppelten die CPU und den FPGA als einzelne Chips per QPI auf einem Mainboard.

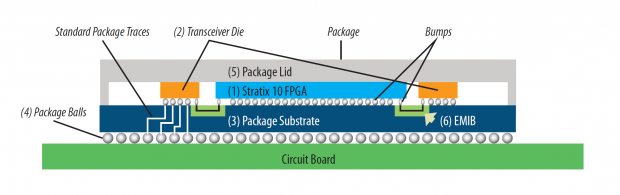

Das neue Modell hingegen verbindet den Xeon E5 und den Arria-FPGA als zwei Dies in einem gemeinsamen Package. Das erklärt, warum Intel die 15-Kern-Variante von Broadwell-EP nutzt, denn das HCC-Pendant (High Core Count) wäre vermutlich zu groß. Was unklar bleibt, ist die Anbindung der beiden Chips im Package. Eine Idee wäre Intels EMIB, die im Herbst 2015 ein bisschen unter dem Radar vorgestellte Embedded Multi Die Interconnect Bridge (PDF).

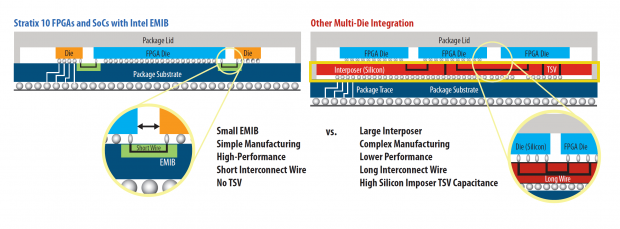

Intel preist diese Technik als Alternative zu Interposer-basierten Packages an, wie sie beispielsweise AMD bei der Fury X mit Fiji-GPU und High Bandwidth Memory nutzt. Die EMIB verbindet die Dies nur an vergleichsweise wenigen Kontakten durch kleine Brücken, was einfacher und günstiger herzustellen sein soll als ein Interposer mit Micro-Bumps und TSVs, der eventuell nicht genug Platz für alle Dies bietet. Möglicherweise ist genau das Intels Problem.

Die Xeon-FPGA-Kombos sollen 2016 als Off-Roadmap-SKUs verfügbar sein.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

Zwischen jetzt und 1994 liegt ein langer Zeitraum - und da kann (und hat) sich sehr viel...