CPU-Architektur: Intels Skylake decodiert und rechnet mehr in einem Rutsch

Der Programmierleitfaden für Intels CPU-Architekturen zeigt: Die Skylake-Technik wurde im Frontend aufgebohrt, um mehr Befehle pro Takt zu den zusätzlichen Ausführungseinheiten zu schicken. Die Caches reagieren zwar langsamer, übertragen aber dann mehr Daten.

Intel hat seinen Programmierleitfaden für die hauseigenen CPU-Architekturen aktualisiert und um die Skylake-Technik erweitert (PDF). Dem Dokument zufolge hat Intel bei der neuen Architektur vor allem das Frontend überarbeitet und an der Geschwindigkeit der Caches gearbeitet, das Backend hingegen entspricht entgegen bisheriger Aussagen der Haswell-Architektur.

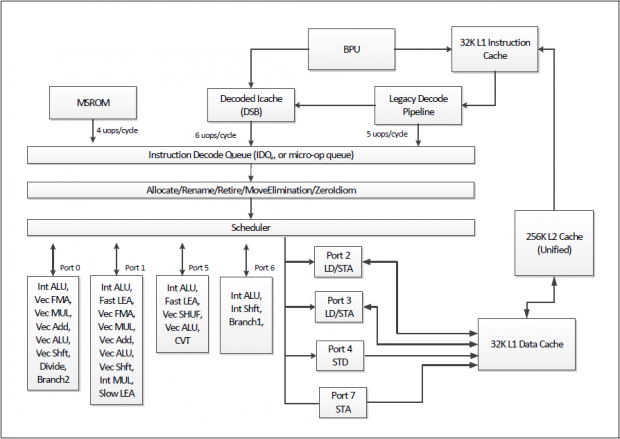

Im Frontend sind wie gehabt vier Decoder verbaut, die herbeigeholte Instruktionen in Mikrobefehle umarbeiten. Anders als alle Core-Architekturen ab Haswell kann die Skylake-Technik allerdings fünf bis sechs statt vier Mikrobefehle (µOps) pro Taktzyklus decodieren. Wenn Intel jedoch von µOps spricht, sind damit teilweise verschmolzene Assembler-Befehle gemeint, die Intel Macro- statt Micro-Ops nennt und seit der Core-Architektur verwendet.

Die Caches, aus denen das Frontend seine Daten bezieht, hat Intel stark verbessert - das zeigte bereits unser Test. Die Dokumentation verrät, dass die höhere Geschwindigkeit nicht von ungefähr kommt: Zwar ist die Transferrate der Puffer massiv angestiegen, die Latenzen aber auch. Bis der L2-Puffer reagiert, dauert es bei Skylake im besten Fall 12 Taktzyklen, bei Haswell nur 11. Auch der L3-Cache braucht bei der Zugriffsdauer etwas länger als bei Haswell, hier sind es im besten Fall 44 statt 34 Zyklen.

Verglichen mit Haswell ergeben die flotteren Caches und das beschleunigte Frontend Sinn, da bei dieser Architektur die Anzahl der Scheduler-Ports und der angeschlossenen Funktionseinheiten erhöht wurde. Dazu zählte eine vierte Integer-ALU, die in dieser Form auch bei Skylake vorhanden ist - durch die schnellere Datenanlieferung bekommt das Rechenwerk nun mehr Arbeit ab. Das ist beispielsweise für Hyperthreading (SMT) interessant.

Mehr Ports oder Funktionseinheiten gibt es bei Skylake ebenfalls - ein Punkt, über den Intel bisher nicht sprechen wollte. Neu sind eine weitere Vector-Shift- und eine Multiplikationseinheit. Instruktionen wie (v)pmul sind allerdings für AVX-Berechnungen gedacht, wovon nur wenige Programme profitieren. Das ist bei vergleichsweise neuen Befehlssätzen allerdings üblich.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

3 Wochen, nachdem der Thread eigentlich schon ausgelutscht ist, diese Aussage zu bringen...

Das hängt von der Qualität und der geforderten Geschwindigkeit ab. H265 und VP9 sind...