Xeon Phi: Knights Landing verfügt über 76 Kerne

Mehr Rechenkerne als bisher bekannt: Intels Xeon Phi Knights Landing integriert 76 statt 72 Silvermont-Cores. Mindestens vier davon werden zugunsten der Ausbeute deaktiviert, da die 14-nm-Fertigung für solch riesige Dies noch zu viele fehlerhafte Chips auswirft.

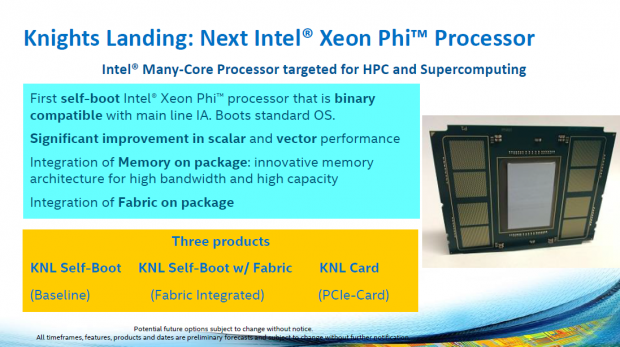

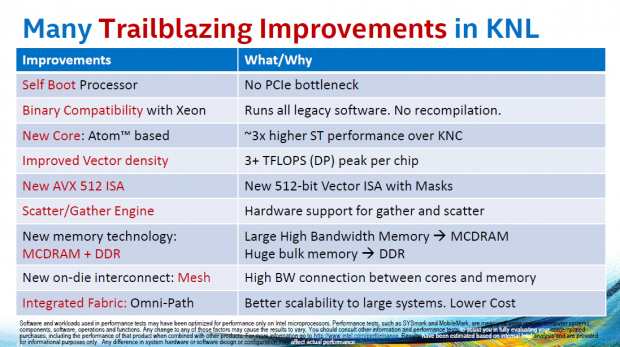

Intel hat auf der Technologie-Tagung Hot Chips 27 neue Informationen zur kommenden Xeon-Phi-Generation, Codename Knights Landing, veröffentlicht. Physikalisch verfügen die als gesockelte Prozessoren entworfenen oder auf Beschleunigerkarten verbauten Chips über 76 Kerne. Mindestens vier davon werden zugunsten der Ausbeute (Yield Rate) - also der voll funktionsfähigen Dies pro Wafer - abgeschaltet. Verfügbar soll Xeon Phi Knights Landing nur mit bis zu 72 aktivierten Silvermont-Kernen sein.

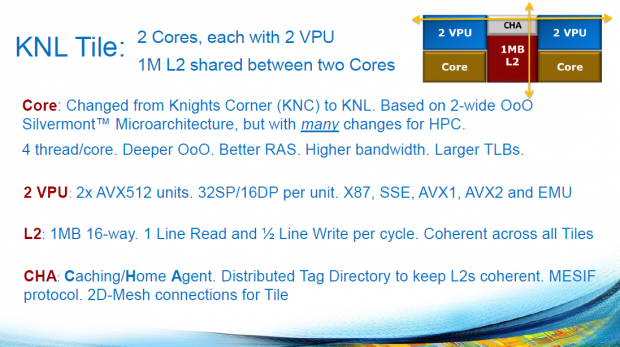

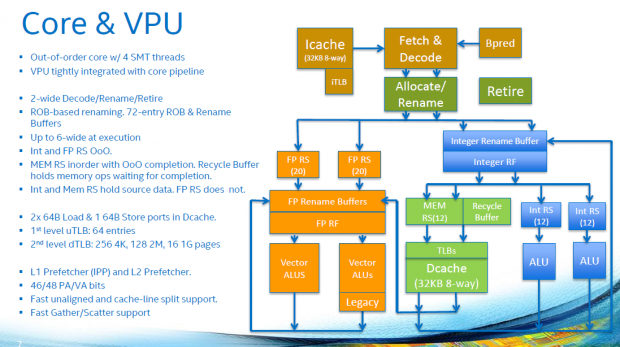

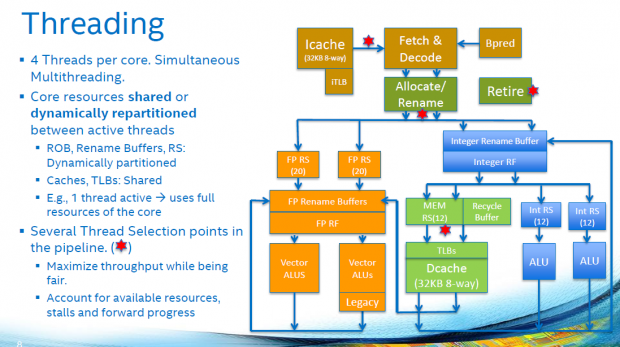

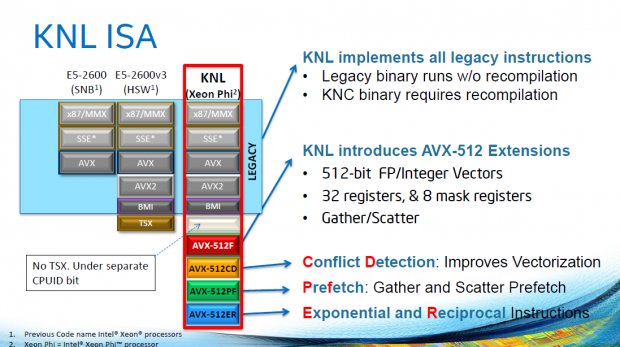

Die einzelnen Rechenwerke bei Knights Landing haben mit den Silvermont-Cores von Bay Trail für Tablets nicht mehr viel gemein: Der L1-Instruktionen-Cache fasst wie gehabt 32 KByte, der L1-Daten-Puffer wuchs von 24 auf 32 KByte an, die TLBs sind größer und das OoO-Fenster wurde verdoppelt. Die zweite Cache-Stufe sichert bei Knights Landing 1 MByte (inklusive L1D), die Kerne sind in der Lage, vier Aufgaben via Hyperthreading parallel zu bearbeiten. Die neben den Kernen sitzenden, auch auf den L2-Puffer zugreifenden Vector Processing Units berechnen erstmals AVX-512-Befehle.

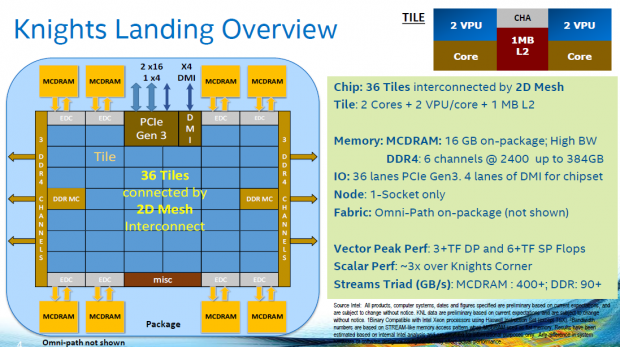

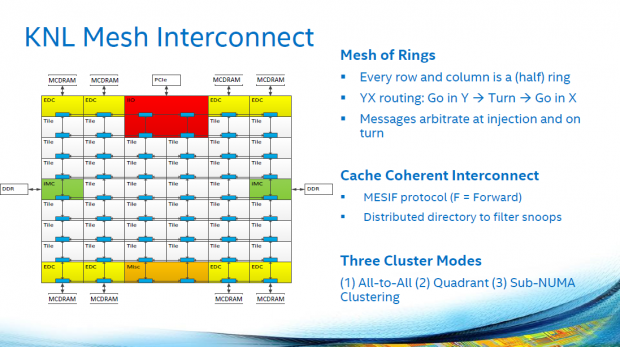

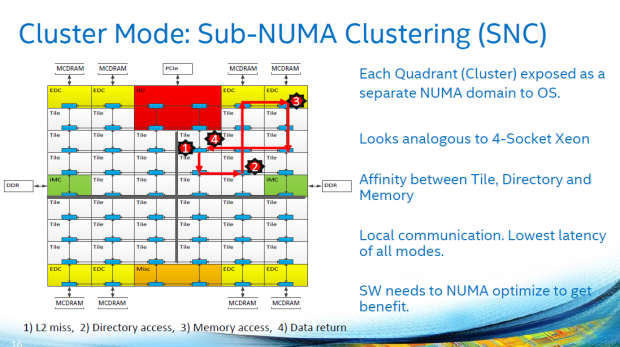

Zwei Kerne und vier VPUs bilden eine Kachel (Tile), von denen 38 Stück in einer Gitterstruktur angeordnet sind. Mit im Knights Landing sitzen acht Speichercontroller, an jeden ist ein 2 GByte fassender MCRAM angeschlossen. Der Speicher stellt eine modifizierte Version von Microns Hybrid Memory Cubes dar, die unterschiedlich angesprochen werden können.

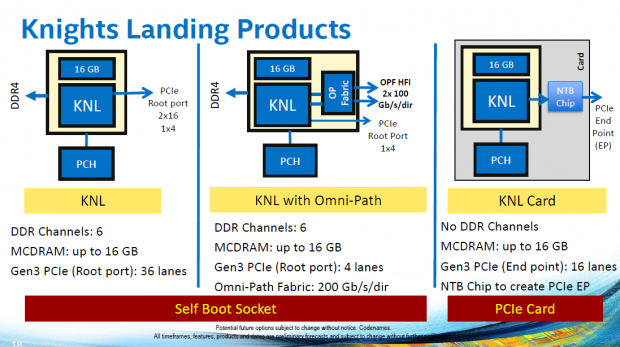

Vor diesem Hintergrund ist wichtig, dass Knights Landing entweder auf Beschleunigerkarten verlötet wird oder auf ein Package gesetzt und als bootbarer x86-Prozessor fungiert. Ist Letzteres der Fall, steuert der Chip zusätzliche 384 GByte an, aufgeteilt auf sechs Speicherkanäle mit je einem DDR4-2400-Modul. Das 192-Bit-Interface liefert 115 GByte pro Sekunde.

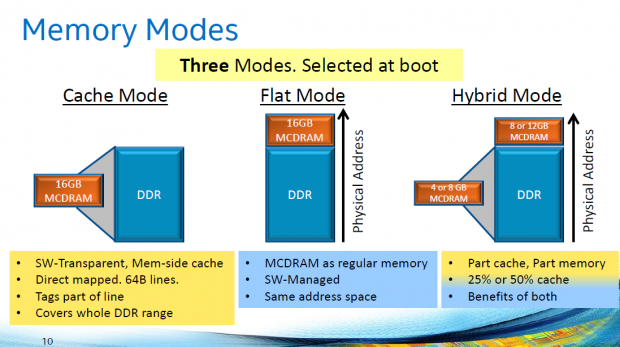

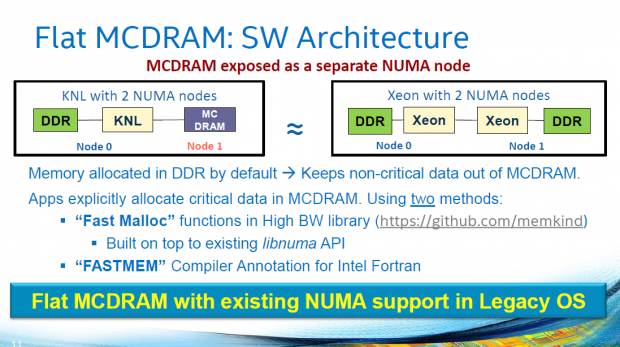

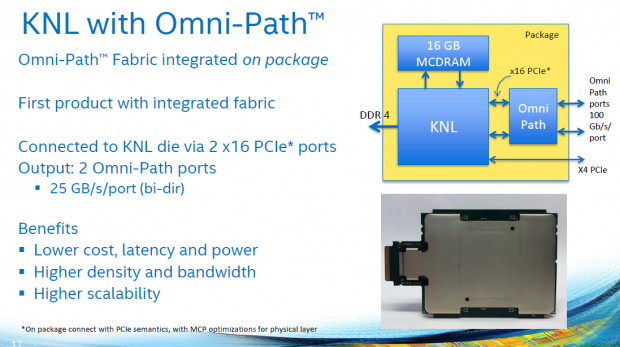

Als gesockelte CPU kann Knights Landing den Speicher in Hardware als Cache (MCRAM) unnd DDR4-RAM ansprechen. Im Flat-Mode muss der Entwickler die Allokation selbst vornehmen und sich im Hybrid-Mode entscheiden, ob 4 oder 8 der 16 GByte MCRAM als Cache dienen. Soll mehr als eine CPU rechnen, ist ein Knights Landing mit einem Omni-Path-Controller notwendig.

Der ist - anders als Infiniband beim Sonoma - nicht im Chip integriert, sondern sitzt mit auf dem sehr ausladenden Package. Angebunden wird die Schnittstelle mit 32 der 36 PCIe-3.0-Lanes, die Datentransferrate beträgt Intel zufolge rund 25 GByte pro Sekunde. Der Chipsatz (Platform Controller Hub, PCH) ist immer per DMI mit vier zusätzlichen PCIe-3.0-Lanes angebunden.

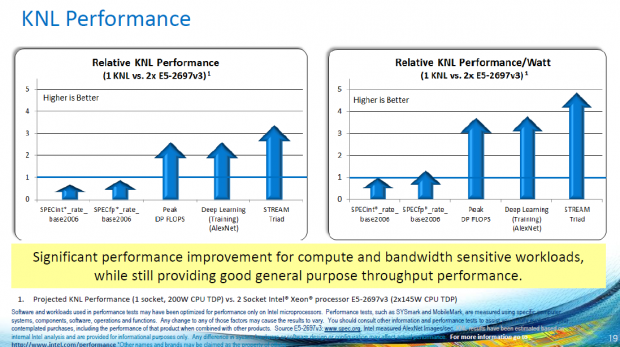

Bei der Leistung von Knights Landing spricht Intel von über 3 Tflops bei doppelter Genauigkeit, was bei 144 AVX-Einheiten mindestens 1,3 GHz bedeutet. Verglichen mit zwei Xeon E5-2697 v3 mit jeweils 14 Kernen bei 2,6 GHz aufwärts schneiden die kommenden Xeon Phi wie erwartet ab: Bei SPECint_2006_rate und SPECfp_2006_rate rechnet Knights Landing langsamer. Die theoretische DP-Leistung, die Datentransferrate und die Geschwindigkeit bei Deep-Learning-Training-Algorithmen liegen höher.

Ziemlich unsinnig sind Intels Angaben der Leistung pro Watt, da der Hersteller die reale Rechengeschwindigkeit auf die theoretische Thermal Design Power von 200 Watt (Xeon Phi) und 290 Watt (2x Xeon E5) umlegt.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

ich frag mich manchmal was einem die schulmeisterei bringt ? was passiert in euch...

wenn du einen mit 72 aktiven kernen kaufst, dann sind auch 72 aktiv...