Serverprozessor: Intel zeigt Xeon E5 mit Altera-FPGA

Das ging flott: Kaum hat Intel Altera gekauft, liefert der Hersteller erste Testsysteme mit Xeon-Prozessoren und Stratix-FPGAs aus. Noch sind es zwei einzelne Chips, künftig möchte Intel beide kombinieren.

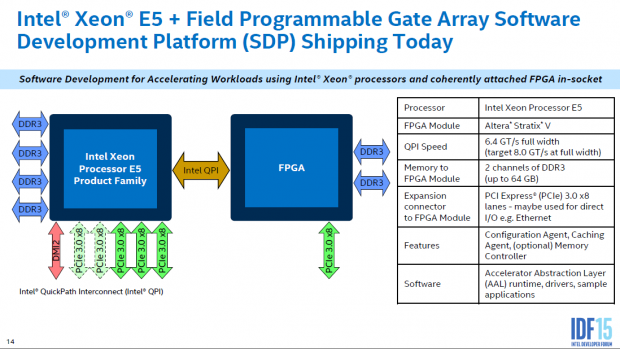

Intel hat auf dem IDF 2015 erste Systeme mit einem Xeon-E5-Chip und einem Stratix-FPGA von Altera gezeigt. Die Kombination aus Serverprozessor und programmierbarer Schaltung (FPGA, Field Programmable Gate Array) soll die Leistung und Effizienz in Datenzentren von Cloud-Anbietern steigern, ohne die Hardwarekosten zu sehr nach oben zu treiben.

Die Idee, x86-CPUs mit FPGAs zu koppeln, hatte Intel bereits 2014 angekündigt und sich anschließend viele Wochen lang mit Altera besprochen. Nachdem Intel zwischenzeitlich mit eASIC kooperierte, übernahm das Unternehmen dann doch den FPGA-Spezialisten Altera für knapp 17 Milliarden US-Dollar. Vorerst liefert Intel spezielle Software-Development-Plattformen an Entwickler aus, damit sich diese mit den Besonderheiten der Systeme vertraut machen können.

Verglichen mit einem x86-Prozessor sind FPGAs zwar kostenintensiver in der Anschaffung, erledigen aber - da es sich um in Hardware programmierbare Schaltungen handelt - bestimmte Aufgaben schneller bei geringerer Leistungsaufnahme. Noch flotter und teurer sind anwendungsspezifische Schaltungen (ASIC), die fest verdrahtete Funktionen aufweisen und damit nur für sehr spezielle Anwendungsszenarien verwendet werden können.

Aktuell stecken in einer Software Development Platform ein Xeon E5 v2 (Ivy Bridge EP) oder v3 (Haswell-EP) und ein nicht näher bezeichneter FPGA von Typ Stratix V. Beide Chips sind durch die QPI-Schnittstelle verbunden, die Intel auch verwendet, um Xeons in Multi-Sockel-Systemen zu koppeln.

Künftig möchte der Hersteller x86-Prozessoren und FPGAs auf ein Package setzen und später beide in einem System-on-a-Chip kombinieren. Erste Produkte erwartet Intel für Anfang 2016.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

dann lohnt es sich wohl sich mal in die Richtung beruflich weiterzubilden, ich werde es...