MIT: Forschungschip vernetzt 36 Cores mit hierarchischem Netzwerk

Busse sind out, ein Netzwerk im Inneren eines Dies ist in: Das meint das MIT, das einen Prozessor mit neuartiger Vernetzung entwickelt hat. Das Konzept erinnert frappierend an ein früheres experimentelles Design von Intel. Die Schaltung des MIT-Chips soll demnächst als Open Source veröffentlicht werden.

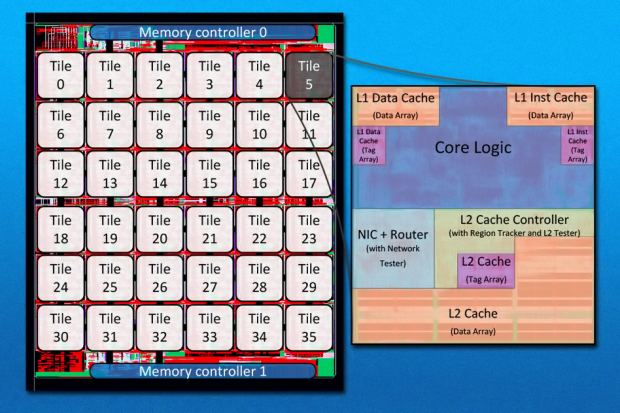

Forscher des Massachusetts Institute of Technology (MIT) haben einen Scorpio genannten Prozessor mit 36 Kernen entwickelt. Dabei setzen sie nicht auf direkte Verbindungen zwischen den Cores untereinander, sondern auf ein Netzwerk. Jeder der Kerne, im Blockdiagramm "Tile" genannt, besitzt dafür einen eigenen Router.

Das dadurch aufgespannte Netz ermöglicht es, dass jeder Kern jeden anderen ansprechen kann. Ganz wie beim Routing im Internet sind die Wege dafür nicht fest vorgegeben, das Netzwerk kann je nach Auslastung der einzelnen Kerne und Router die Pfade jederzeit selbst bestimmen. Das sorgt für weniger Aufwand bei der Verschaltung der Kerne als mit den bisherigen breit ausgeführten Bussen, zudem belegt die Kommunikation von einem Kern mit einem anderen stets den gesamten Bus - die anderen müssen warten.

Da die Kerne des MIT-Chips gemeinsam an Aufgaben rechnen sollen, müssen die Inhalte ihrer Caches aber kohärent gehalten werden. Die üblichen Methoden des Lauschens am Bus, auch "Snooping" genannt, sind dafür aber nicht mehr effizient: Daten werden in einem mit Routing vernetzten Chip nicht definiert von Punkt zu Punkt übertragen, jeder Core müsste ständig wissen, was jeder andere tut. Das Netzwerkaufkommen wäre mit 36 Kernen dafür viel zu hoch.

Deshalb gibt es ein zweites Netzwerk, das keine Nutzdaten überträgt. Es arbeitet vom übergeordneten Routing-Netz unabhängig und meldet an alle Kerne stets nur, welcher Core gerade Daten übertragen hat. Offenbar wird dieser dann bis zum Abschluss der Aufgabe mit niedriger Priorität behandelt und kann das Routing nicht mehr stören.

Damit organisiert sich das Netzwerk ständig selbst hierarchisch neu, es soll damit sehr effizient arbeiten. Zur Architektur der einzelnen Kerne und den Takten macht das MIT bisher keine Angaben, es handelt sich laut dem Blockdiagramm aber um eine recht moderne CPU mit L1-Caches für Daten und Befehle und einem L2-Cache für jeden einzelnen Kern. Wenn weitere Tests mit Prototypen-Chips erfolgreich sind, will das MIT das Design in der Beschreibungssprache Verilog veröffentlichen und unter Open Source stellen, sodass andere den Chip nachbauen können.

Die Vernetzung mittels Routern auf jedem einzelnen Kern hatte Intel bereits 2007 mit seinem Forschungschip 'Polaris' vorgestellt. Im Jahr 2010 wurde der inzwischen "Single Chip Cloud Computer" (SCC) getaufte Baustein auch an Bildungseinrichtungen ausgeliefert. Ob das MIT-Design Verbindungen zum SCC aufweist, konnte Intel auf Anfrage von Golem.de nicht unmittelbar beantworten.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed