Ivy Bridge-EX: Intels Xeon E7-v2 mit 15 Kernen und drei Ringbussen

Als Serie E7-4000 bietet Intel seine neuen Serverprozessoren an. Die Xeons basieren jedoch auf der Ivy-Bridge-Architektur und wurden vor allem durch neue Bussysteme und AVX aufgewertet. Mit nur einem Die kann Intel CPUs von 6 bis 15 Kernen produzieren.

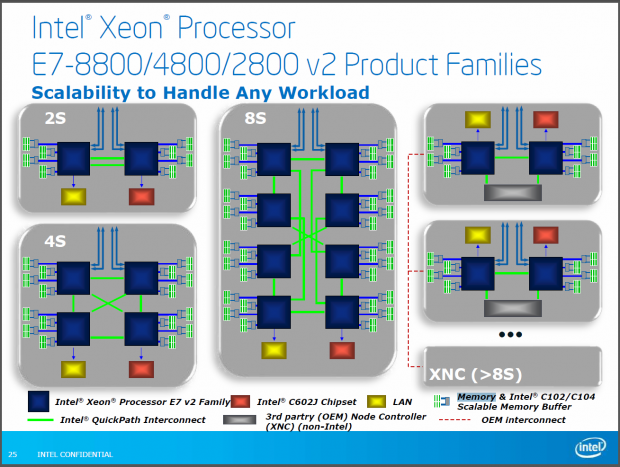

Die bisher unter dem Codenamen Ivy Bridge-EX geführten Prozessoren bietet Intel nun als Serie E7-4000 an. Die gesamte Plattform trug bisher den Codenamen Ivytown. Geläufig ist auch die Bezeichnung E7-v2, denn die CPUs sind die Nachfolger der 2011 eingeführten Serie E7. Wie diese ist auch E7-v2 auf Server mit bis zu acht Sockeln ausgelegt, bei denen möglichst viele vollwertige x86-Kerne parallel arbeiten sollen.

- Ivy Bridge-EX: Intels Xeon E7-v2 mit 15 Kernen und drei Ringbussen

- AVX, PCIe 3.0 und neues QPI

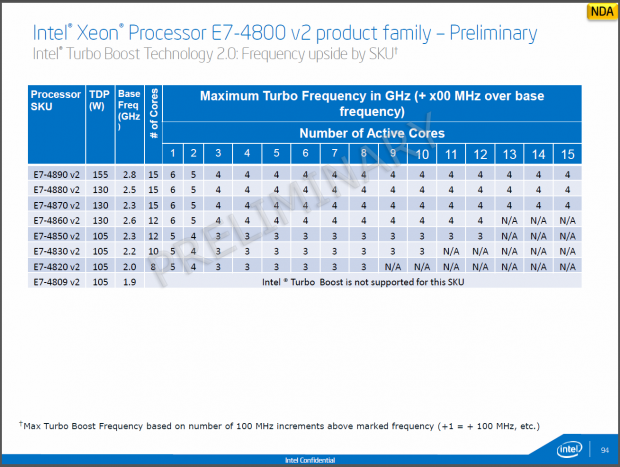

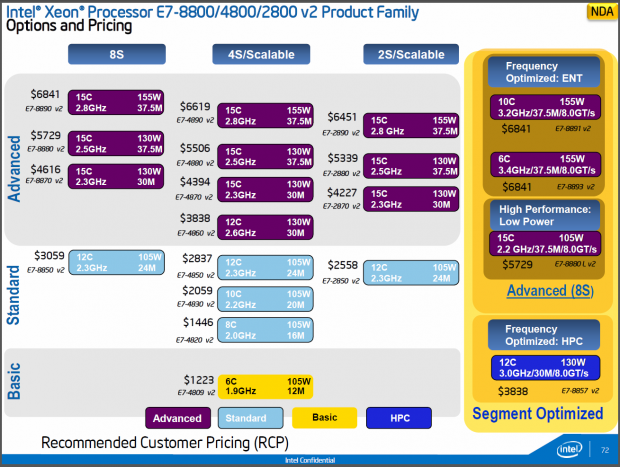

Auch wenn die Modellnummer 4000 eine Nähe zu den Core-i-4000 alias Haswell suggeriert, basieren die Xeons immer auf der vorherigen Desktop-Architektur. Im Falle der E7-v2 ist das Ivy Bridge, Intels erstes Design mit 22 Nanometern Strukturbreite. Durch den inzwischen wohl gut laufenden Fertigungsprozess konnte die Leistungsaufnahme weitgehend gleich bleiben, nur die schnellsten Modelle kommen auf bis zu 155 Watt TDP. Mit dem E-8880 v2 gibt es aber auch einen 15-Kerner, der mit 130 Watt auskommt.

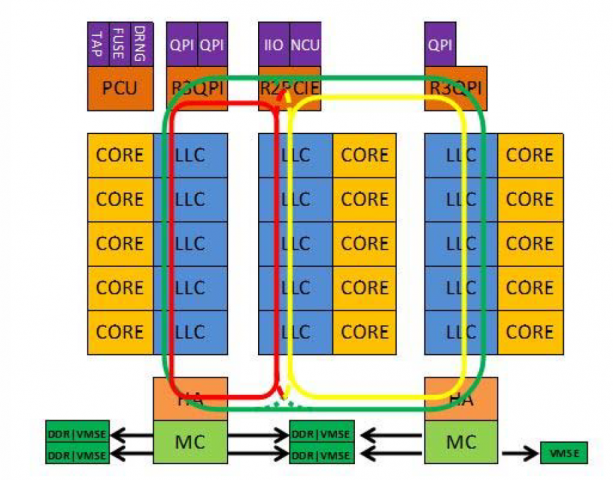

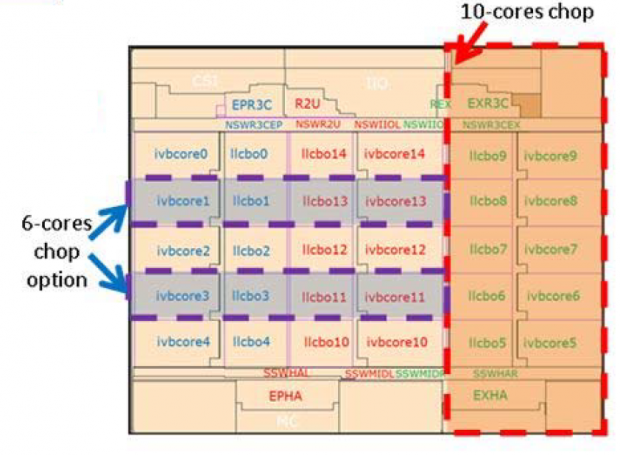

Während die Haswell-CPUs mit verschiedenen Dies gefertigt werden, hat Intel sich für den Xeon E7-v2 nur für eines entschieden. Es bietet drei Blöcke für den L3-Cache, jeder davon ist an drei Einheiten mit bis zu fünf Cores angebunden. Daher ergeben sich flexible Möglichkeiten für die Zahl der Kerne: Sind nur bis zu zehn gefragt, kann der auf den Diagrammen rechts gelegene Block weggelassen werden. Bei weniger als zehn Kernen werden auf dem verbleibenden Die bis zu vier deaktiviert, was einen Sechskerner ergibt. Das ist die kleinste Ausbaustufe von Ivy Bridge-EX.

Auf einer zur Fachkonferenz ISSCC vorgelegten Präsentation spricht Intel dabei von "chop options" - frei übersetzt: den Möglichkeiten, etwas abzuhacken. Zumindest der rechte Block mit fünf Kernen und L3-Cache dürfte bei bis zu zehn Kernen also tatsächlich nicht vorhanden sein. Intel muss also für alle neuen Xeons nur ein Die herstellen und kann die funktionierenden Kerne so konfigurieren, dass sich die gewünschte Zahl der Cores ergibt.

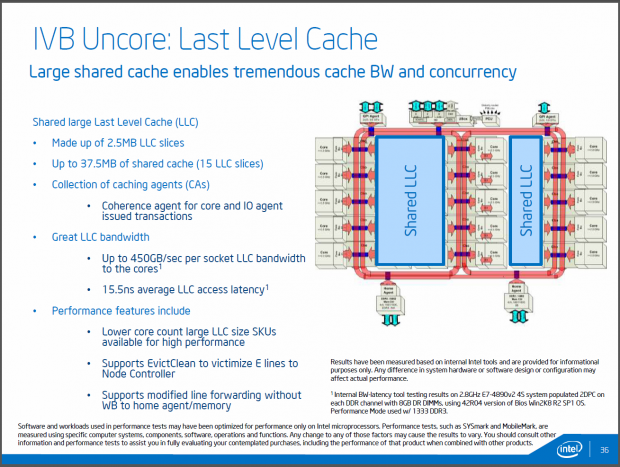

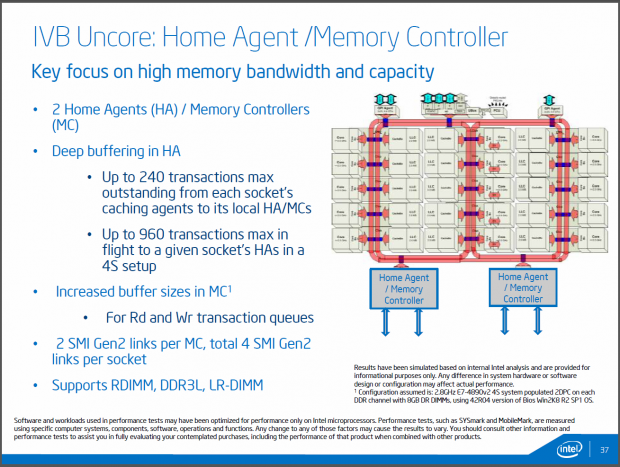

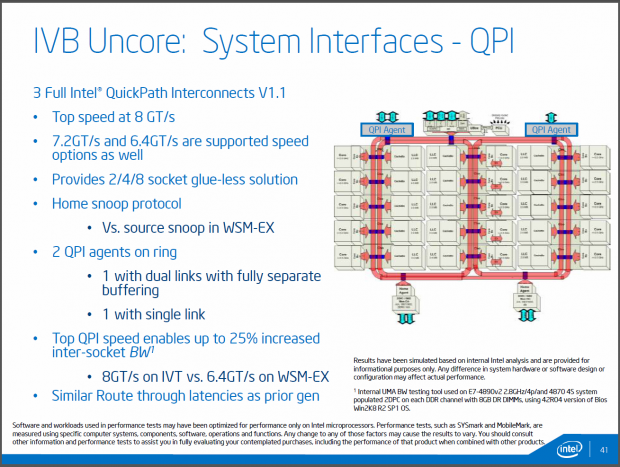

Da es nicht wie bei bisherigen Intel-Designs einen gemeinsamen L3-Cache für alle Cores gibt, können die Kerne auch nicht über einen einzelnen Ringbus kommunizieren. Nötig sind sogar drei, welche eine direkte Verbindung aller drei 5-Kern-Blöcke erlauben. Denn der in der Mitte des Dies gelegene L3-Cache kann mit dem links danebenliegenden direkt Daten austauschen. Die drei Ringbusse werden durch zwei Home Agents kontrolliert mit je zwei Speichercontrollern, während es bei den Desktop- und Mobil-CPUs seit Sandy Bridge stets nur einen solchen Controller für Bus und Speicherschnittstellen gab. Insgesamt können die Caches bei einem voll ausgebauten E7 v2 bis zu 37,5 MByte groß sein, ein gesamter neuer Xeon besteht aus bis zu 4,3 Milliarden Transistoren.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

| AVX, PCIe 3.0 und neues QPI |

- 1

- 2

Nicht mal da... aber nicht aus Protest, sondern weil Intel ab Sandy Bridge so ein Brett...