Chinesischer Forschungschip: 16-Core-CPU mit Message Passing

Auf der Fachkonferenz ISSCC haben chinesische Forscher einen RISC-Prozessor mit 16 Kernen vorgestellt. Statt mit herkömmlicher Speicherverwaltung arbeitet das Design mit Message Passing, das per Hardware gesteuert wird. Ziel sind effizientere Supercomputer.

Wissenschaftler der staatlichen chinesischen Universität Fudan in Schanghai haben Prototypen einer RISC-CPU mit 16 Kernen gebaut. Das Design, das laut Semiaccurate auf der ISSCC in San Francisco vorgestellt wurde, unterscheidet sich von den bekannten Godson-Prozessoren, die einige von Chinas Supercomputern antreiben.

Im Gegensatz zu herkömmlichen Mehrkern-CPUs, bei denen sich die Cores gemeinsame Speicherbereiche teilen, arbeitet der Fudan-Prozessor mit Message Passing. Dabei gibt es je nach Implementierung keine fest zugeordneten Speicherbereiche, die Kerne tauschen über Nachrichten aus, welche Adressen sie belegen wollen. Ein konkurrierender Zugriff ist dadurch jederzeit möglich - wer zuerst kommt, alloziert zuerst.

Message Passing ist bei Supercomputern, beispielsweise über Infiniband, schon lange Realität. Die Implementierung erfolgt aber in Software und kann die Speichermechanismen der CPU nicht aushebeln. Die Fudan-CPU erledigt die Funktion per Hardware.

3-x-3-Matrix mit dediziertem Kern für Speicherfunktionen

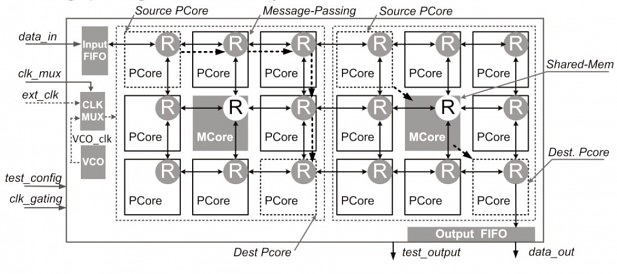

Dazu gibt es zwei Module mit je neun Kernen, die wie eine 3-x-3-Matrix angeordnet sind. Der mittlere Kern steuert die Speicherbelegung, die Messages können aber auch direkt von jedem Kern zu jedem anderen durch die anderen hindurchgeschickt werden. Das erinnert im Layout an Intels SCC, der ebenfalls mit einer Vernetzung von Kernen arbeitet - von Message Passing hat Intel für sein Design aber bisher noch nicht gesprochen.

Zudem soll der chinesische Prozessor nicht mehr mit Caches arbeiten, wie das die meisten großen CPUs nach etwa x86- oder Power-Architektur tun. Die Caches, die Speicherzugriffe abfangen, würden bei Message Passing auch eher bremsen. Statt der Zwischenspeicher sollen die Kerne über ein gemeinsames, sehr breites Register-File verfügen.

Die Fudan-CPU ist, ebenso wie der SCC, noch ein Forschungsprojekt. Er wird Semiaccurate zufolge aber bereits bei TSMC in 65 Nanometern Strukturbreite hergestellt und erreicht bis zu 800 MHz pro Kern. Mit dem etwas geringeren Takt von 750 MHz soll er bei nur 1,2 Volt betrieben werden können. Jeder Kern soll dann nur 34 Milliwatt Leistung aufnehmen, was mit sehr kleinen ARM-SoCs vergleichbar ist.

Damit ist auch das Einsatzgebiet abzusehen, es geht offenbar um sehr energieeffiziente Supercomputer mit zigtausenden von Kernen. Das gleiche Ziel verfolgt auch ein neuer Godson, über den EEtimes berichtet. Mit dieser von der MIPS-Architektur entlehnten CPU will China bald einen ersten Supercomputer mit über 1 Petaflops Leistung in Betrieb nehmen, der nur mit Prozessoren aus dem Reich der Mitte bestückt ist.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

Das mag sein. Nur, ob China dann sein Wissen so bereitwilligt mit anderen Ländern teilt...

oder auch sparc oder ppc.

Richtig, schrob ich ja schon oft.. ^^ Danke, ist korrigiert.