Suvolta: Halb so viel Spannung für gleich schnellen Transistor

Das Startup Suvolta will Intel Konkurrenz machen. Zusammen mit Fujitsu hat das Unternehmen ein SRAM hergestellt, dessen Transistoren bei nur 0,425 Volt noch schalten. Möglich macht das eine neue Bauform, die bald für Mobilprozessoren verwendet werden könnte.

Auf der Fachkonferenz IEDM haben Fujitsu und Suvolta den DDC-Transistor vorgestellt. Das Kürzel steht für "deeply depleted channel" und beschreibt eine leicht andere Bauform der bisher am häufigsten verwendeten planaren Transistoren. Anders als Intels Tri-Gate-Transistoren, die auch in die Höhe gebaut sind und von IBM als FinFETs bezeichnet werden, sollen sich die DDC-Transistoren wesentlich günstiger herstellen lassen.

Bisher stellt nur Intel für die kommenden Ivy-Bridge-CPUs dreidimensionale Transistoren in Massenstückzahlen her. Der Großteil der Halbleiterbranche setzt auf die planaren Transistoren. Für diese Bauelemente gilt aber schon seit vielen Jahren eine Spannung von rund 1,0 Volt als die Grenze, bei der die Transistoren noch schalten können.

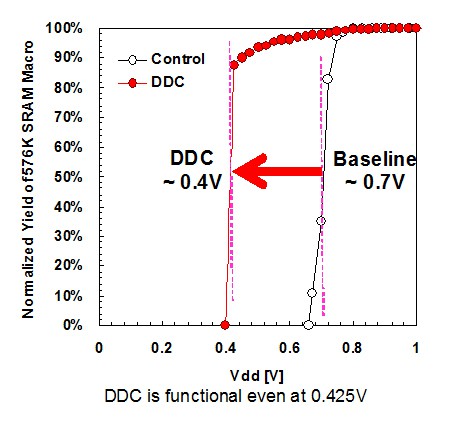

Suvolta hat nun ein Verfahren erfunden, auf dessen Basis Fujtsu ein SRAM bauen konnte, das bei nur 0,425 Volt noch arbeitet. Der Baustein wurde zwar in der für PC-Prozessoren nicht mehr aktuellen Strukturbreite von 65 Nanometern hergestellt, die DDC-Transistoren sollen sich aber mindestens auf 32 Nanometer verkleinern lassen.

Die geringe Spannung wird durch eine neue Struktur des Kanals der Transistoren ermöglicht. Das Silizium wird zunächst weitgehend von Ladungsträgern befreit (depleted) und dann gezielt mit Hilfsmaterialien dotiert. Welche Elemente Suvolta dafür einsetzt, behält das Unternehmen noch für sich, ein gängiger Werkstoff in der aktuellen Technik ist beispielsweise Hafnium.

Schichtweise Dotierung für kontrollierten Ladungsfluss

Durch solche Dotierung verändert sich der Ladungstransport im Transistor und dessen Schaltverhalten. Während bisherige Transistoren aber meist nur mit ein oder zwei Schichten dotiert werden, verwendet Suvolta nach seinen bisher veröffentlichten Informationen mindestens drei. Die Ladung soll sich in der untersten "screening region" genannten Schicht zunächst anreichern und dann durch die anderen Schichten schnell die Schaltschwelle erreichen.

Denn die Geschwindigkeit ist bei geringen Spannungen bisher das Problem neuer Transistoren. Suvoltas Angaben zufolge sollen die DDC-Transistoren mit immerhin 30 Prozent geringerer Spannung bei gleicher Schaltgeschwindigkeit auskommen. Als Spannungsbereich nennt das Unternehmen 0,4 bis 0,7 Volt, gibt die Geschwindigkeiten aber bisher nicht an.

Für mehrere Gigahertz schnelle PC-Prozessoren ist das Verfahren aber auch gar nicht vorgesehen, Suvolta will damit vor allem bei sehr sparsamen Systems-on-a-Chip (SoC) punkten. Diese SoCs stecken in jedem Smartphone, Tablet oder in anderen mobilen Geräten. Die Bausteine werden heute meistens von großen Auftragsherstellern (Foundries) wie TSMC hergestellt, welche mit planaren Transistoren arbeiten.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

Auszüge aus dem Artikel: "Möglich macht das eine neue Bauform, die bald für...

Ich finde, dass es für die bestimmt ein langer weg ist, bis sie koonkurrenzfähig sind...

Kannst vielleicht mal versuchen, den CPU-Kühler durch ein großes Kupferteil zu ersetzen...

... Eierlegenden Wollmilchsäuen, von denen man wahrscheinlich nie wieder was hört...