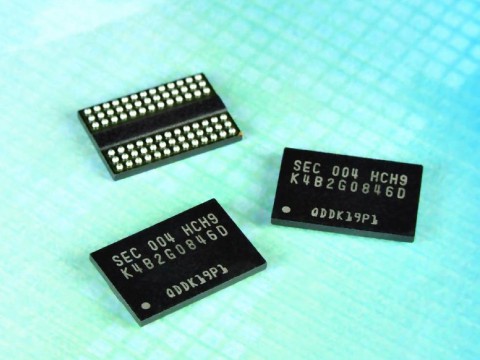

Samsung: Sparsame DDR3-Chips in 30-Nanometertechnik

Herstellungsverfahren soll Produktivität steigern und Energieverbrauch senken

Samsung will DDR3-Speicher künftig in 30-Nanometertechnik fertigen. Erste Tests seien bereits erfolgreich von Kunden evaluiert worden, die Massenproduktion soll in der zweiten Jahreshälfte 2010 starten.

Erste Kunden von Samsung konnten die DDR3-SDRAM-Chips mit einer Kapazität von 2 GBit bereits erfolgreich testen. Samsung erhofft sich von der Umstellung der Produktion eine höhere Produktivität seiner Anlagen und größere Mengen an leistungsfähigen DDR3-Chips mit 1,5 und 1,35 Volt für Server, Desktops und Notebooks.

Die geringere Spannung gegenüber den bisher üblichen 1,5 Volt ist Teil der JEDEC-Standards für DDR3-Speicher, wurde bisher aber nur in Prototypen verwendet. Intels aktuelle Dual-Cores für Notebooks und Desktops können jedoch mit 1,35 Volt für DDR3-Speicher umgehen.

Die Umstellung auf Strukturgrößen von 30 Nanometer steigert die Produktivität im Vergleich mit 40-Nanometer-Prozessen bei der Herstellung von DDR3-Chips um rund 60 Prozent, so Samsung. Auf einem Wafer lassen sich bei kleineren Strukturen mehr Chips fertigen, was die Produktionskosten entsprechend senkt.

Zudem sollen die in 30-Nanometertechnik hergestellten Chips eine geringere Leistungsaufnahme aufweisen. Im Vergleich zu Chips in 50-Nanometertechnik soll der Energiebedarf 30 Prozent geringer ausfallen. So sollen 4 GByte DDR3-Speicher in 30-Nanometertechnik in einem aktuellen Notebook nur mit 3 Watt zu Buche schlagen. Weitere Angaben zu dieser Messung machte Samsung nicht, es dürfte sich aber um ein Core-i-System handeln.

Die Massenproduktion der neuen Chips will Samsung im zweiten Halbjahr 2010 aufnehmen.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed