Intel packt 3 Milliarden 22-nm-Transistoren in ein SRAM

Details zu Intels kommendem 22-Nanometer-Prozess

Intel hat auf dem IDF einige Informationen zu seinem kommenden 22-Nanometer-Prozess gegeben. CEO Paul Otellini zeigte auch einen ersten Wafer, auf dem pro Chip knapp drei Milliarden Transistoren vereint sind.

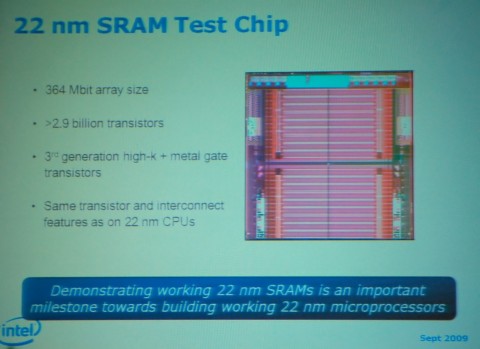

Intel hat mit seinem 22-Nanometer-Prozess ein SRAM-Array mit rund 2,9 Milliarden Transistoren und 364 Megabit Kapazität hergestellt, das bislang größte gefertigte SRAM. Könnte man daraus einen Cache für einen Prozessor bauen, so wäre dieser rund 45 Megabyte groß.

SRAM-Chips (Static Random Access Memory) bilden die Vorstufe von komplexeren Einheiten wie Mikroprozessoren. Die statischen Speicher eignen sich wegen ihrer einheitlichen Struktur auf dem Chip besonders gut als Testvehikel für neue Fertigungsverfahren. Dabei setzt Intel nun die mittlerweile dritte Generation seiner High-K-Metal-Gate-Technik ein, die vor zwei Jahren vorgestellt wurde.

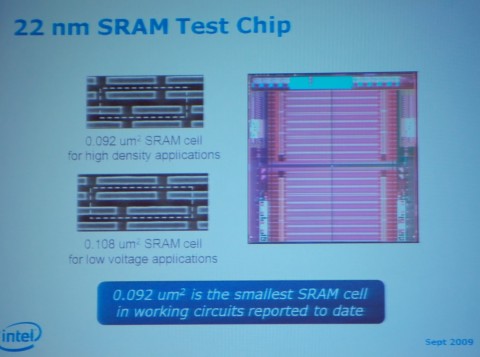

CEO Paul Otellini führte in seiner Keynote-Ansprache einen Wafer mit den 22-Nanometer-Chips vor, Intels Chef der Halbleiterfertigung, Mark Bohr, verriet im Anschluss noch einige Details über den Chip. Intel hat darauf SRAM-Zellen in zwei Größen verbaut, die eine für schnelleres Schalten, die andere für möglichst geringe Leistungsaufnahme. Letztere 6T-Zelle ist mit 0,092 Quadratmikrometer laut Bohr die kleinste SRAM-Zelle, die bisher gebaut wurde. Allzu weit soll der Chip nicht vom Prozessorbau entfernt sein: Die Transistoren und deren Interconnects sind auf dieselbe Art gebaut, wie sie auch in 22-Nanometer-CPUs zum Einsatz kommen soll.

Diese 22nm-Prozessoren sollen in der zweiten Hälfte des Jahres 2011 auf den Markt kommen, das CPU-Design "Sandy Bridge" ist bereits fertig. Es folgt den ersten 32-nm-CPUs der Westmere-Familie, die Ende 2009 und Anfang 2010 zuerst für Notebooks und dann für Desktops erscheinen sollen.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed