Tile64: 64-Kern-CPU für Netze und Medien jetzt lieferbar

Einfache Programmierung mit Linux, neuartige Vernetzung der Kerne

Einer der ersten verfügbaren Manycore-Prozessoren kommt von einem kleinen US-Start-up, das von einem MIT-Professor gegründet wurde. Die CPU "TILE64" besteht aus 64 Kernen, die über ein Mesh-Netzwerk verknüpft sind. Anwendungen dafür sieht der Hersteller bei Netzwerkgeräten und Multimedia-Produkten.

Der Tile64 ist kein PC-Prozessor - vielmehr sieht ihn der Hersteller Tilera im Embedded-Bereich, also mit speziellen Anwendungen für Hardware, die einmal fest eingebaut wird und dann Jahre oder Jahrzehnte laufen soll. Über die Funktionsweise der Kerne schweigt sich Tilera noch aus, vermutlich handelt es sich aber um stark abgespeckte Einheiten eines MIPS-Designs. Der Gründer von Tilera, MIT-Professor Anant Agarwal, experimentiert seit zehn Jahren mit Mehrkern-Prozessoren und stellte am MIT im Jahr 2003 das Projekt 'Raw' vor. Bereits 1983 war Argawal am Design des ersten MIPS-Prozessors beteiligt.

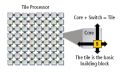

Ein Switch auf jedem Kern

Die 64 Kerne des Tile64 sind nicht über einen Bus verbunden, sondern über ein Netzwerk, das Tilera "iMesh" nennt. Auf jedem Kern sitzen L1- und L2-Caches unbekannter Größe sowie ein Switch, der wie das gleichnamige Netzwerkgerät arbeitet. Die Switches können Daten und Instruktionen direkt zu einem anderen Kern durchschalten. Zudem gibt es noch einen L3-Cache, den sich die Kerne teilen. Diese Lösung ähnelt verblüffend Intels Design-Studie "Polaris", wo 80 Kerne über ein Mesh-Netzwerk mit Switches verbunden wurden. Soll aus Polaris laut Intel nie ein Produkt werden, so ist der Tile64 laut Tilera aber bereits lieferbar.

Neben dem Mesh hat Tilera für das Gesamtkonstrukt auch umfangreiche I/O-Funktionen vorgesehen - ganz wie Suns Ultrasparc T2. Vier Speichercontroller für DDR2 stehen zur Verfügung, dazu kommen zwei PCIe-Ports mit 10 Gigabit/s sowie zwei Ports für Gigabit-Ethernet und als Krönung zwei weitere Ports für 10-Gigabit-Ethernet. Diese beiden Ports hat auch der Ultrasparc T2 auf dem Die, er ist jedoch als eher universeller Server-Prozessor ausgelegt.

Programmiert wird der Tile64 unter Linux, Standard-SMP-Code soll problemlos auf dem Prozessor laufen. Tilera hat dafür einen ANSI-C-Compiler geschrieben. Will man die Anwendungen weiter optimieren, gibt es Netzwerk-Bibliotheken für das Mesh des Tile64, mit denen sich ein Load-Balancing für die einzelnen Kerne erreichen lässt.

In einem Netzwerkgerät soll der Tile64 auf den Layern 4 bis 7 einen Durchsatz von 20 Gigabit pro Sekunde erreichen; steckt man ihn beispielsweise in eine Set-Top-Box, soll der Prozessor zwei H.264-Datenströme für HD-Videos parallel kodieren können. Beim Video-Conferencing mit HD-Strömen sollen es zehn Bildverbindungen parallel sein.

Noch vollmundiger sind die Versprechungen zur Leistungsaufnahme: Auf 170 Milliwatt pro Kern lässt sich die Leistungsaufnahme drücken, 30-mal besser soll die "Performance pro Watt" gegenüber einem Dual-Core-Xeon von Intel sein. Dieses extreme Verhältnis ist aber nicht zum Spartarif zu haben: Tilera gibt einen Preis von 435,- US-Dollar für den kleinsten Tile-Prozessor an, wenn man gleich 10.000 Stück abnimmt. Lieferbar sollen ab sofort drei verschieden schnell getaktete Versionen des Prozessors von 600 MHz bis 1 GHz sein, die sich zudem in der I/O-Ausstattung unterscheiden. Zudem will das Unternehmen auch Varianten mit 36 und 120 Kernen entwickeln.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

Bei 4GB ist mit 32Bit unter Windows (zumindest Server 2003 Ent.) nicht Schluss -> PAE...

Wohl eher der Anwalt der Firma iMesh. http://en.wikipedia.org/wiki/iMesh

Dann nehm ich bei CS ein Spray-Logo mit dem Bild der hässlichsten Frau, das ich finden...