IDF: Erste Details zur neuen Intel-Architektur

Breite, aber kurze Pipeline mit 14 Stufen

Stück für Stück hat Intel am ersten Tag des IDF Fall 2005 die ersten Details zu der noch namenlosen Mikro-Architektur preisgegeben, die im zweiten Halbjahr 2006 die bisherigen CPUs für Server, Desktops und Mobilrechner ablösen soll. Wie versprochen stehen Takteffizienz und eine kürzere Pipeline im Mittelpunkt - HyperThreading bleibt hingegen vorerst außen vor.

Hatte Intel im Vorfeld der Markteinführung des Pentium 4 Ende 2000 noch mit griffigen Marketing-Schlagworten wie "Netburst", "TraceCache" oder "Rapid Execution Engine" nur so um sich geworfen, gibt es nun noch nicht einmal einen Codenamen der neuen Architektur, die Netburst beerben soll. Wohl auch, weil Intel bereits im Mai 2005 erste Hinweise auf eine neue Architektur gab, hatten offenbar einige Journalisten mehr als das in San Francisco Gebotene erwartet.

- IDF: Erste Details zur neuen Intel-Architektur

- IDF: Erste Details zur neuen Intel-Architektur

- IDF: Erste Details zur neuen Intel-Architektur

- IDF: Erste Details zur neuen Intel-Architektur

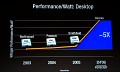

Mehr Leistung pro Watt

In der vorvergangene Woche nochmals eigens durch Intel angekündigten Keynote des neuen CEO Paul Otellini war am Morgen (Ortszeit) zunächst buchstäblich nichts Neues zu erfahren - außer, dass Intel sich jetzt auf allen Plattformen dem Stromsparen verschrieben hat. Dass die neue Architektur in Chips mit Codenamen Merom (Notebooks), Conroe (Desktops) und Woodcrest (Server) zum Einsatz kommen soll, war bereits seit Mai bekannt. Diese Informationen fasst Otellini nochmals in einer einzigen Folie zusammen. Immerhin wickelte er den ersten Teil der Präsentation auf einem Merom-Notebook ab.

Im anschließend als "Mega-Briefing" angekündigten Vortrag, zu dem nur die Presse geladen war, passten die neuen Informationen über die neue Intel-Architektur dann ebenfalls auf eine einzelne Folie. So soll die Pipeline mit 14 Stufen gegenüber der extrem langen Pipe des aktuellen Prescott-Kerns mit 31 Stufen stark verkürzt werden. Dafür passen nun vier Befehle in die Pipe, die dadurch weiter und effizienter wird. Das gefürchtete "Stalling", bei dem die Pipeline durch falsche spekulative Ausführungen eher zur Bremse als zum Beschleuniger wird, soll dadurch deutlich seltener auftreten. Diese "Out of Order Execution", eine der zentralen Leistungsquellen aller modernen x86-Prozessoren, wird dadurch laut Intel deutlich effektiver.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

| IDF: Erste Details zur neuen Intel-Architektur |

Also ich bin mir sicher das es einen neuen Socket geben wird, bis jetzt waren neue CPU...

Ah, "immer wieder" mh also irgendwie ist AMD erst seit kurzem einigermaßen am Markt...

*Keksgeb*

Naja, was verkauft Apple und was verkauft Intel. Ich muss sagen dass Intel sich für...