Reverse Engineering: Signale auslesen an bunten Pins

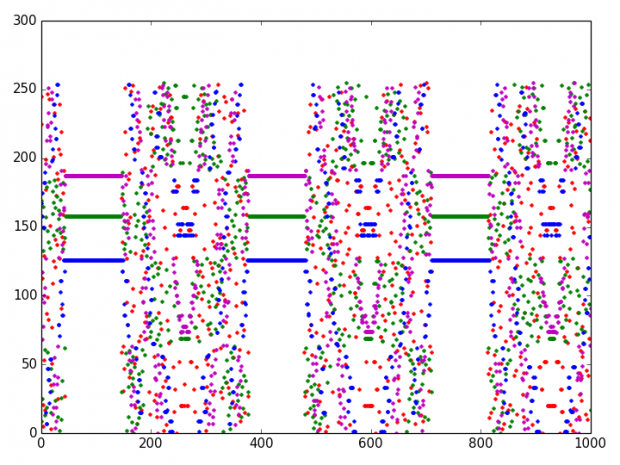

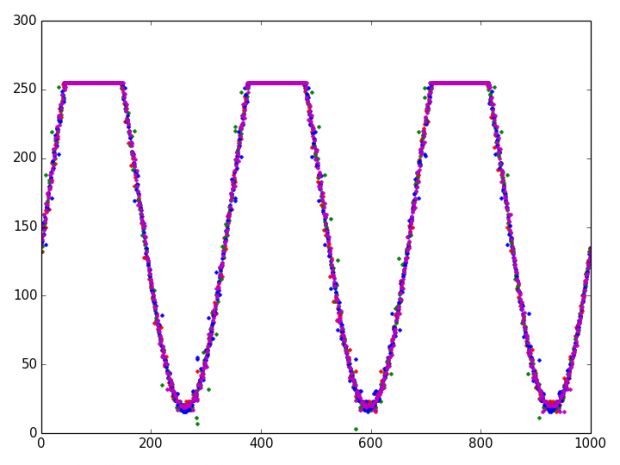

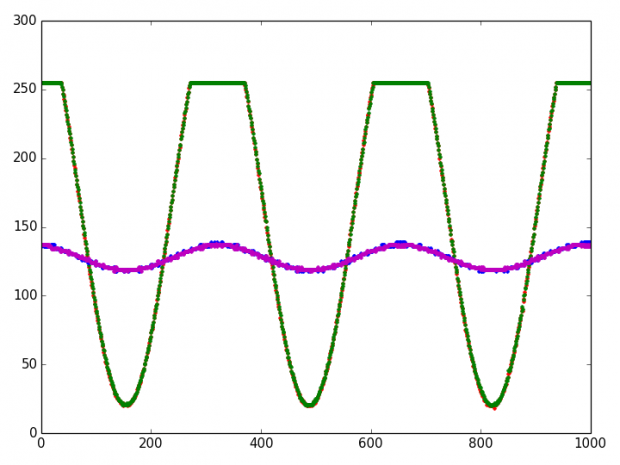

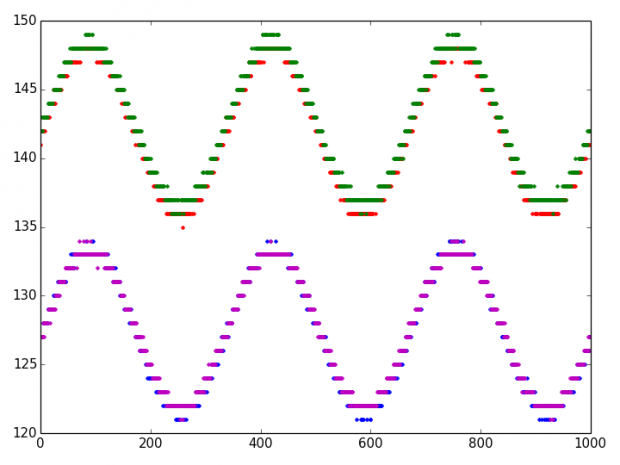

Die Übersicht über 256 Pins zu behalten, ist schwer. Deswegen greifen wir zum Malstift. Zur Belohnung zeigt uns Linux schließlich hübsche Sinuskurven.

Eine Vielzahl von GPIO-Pins des FPGA eines Oszilloskops kenne ich seit dem vierten Teil der Artikelserie, doch es ist nicht einfach, die Übersicht zu behalten und mir zu merken, welcher Pin wofür zuständig ist. Deshalb werde ich mir im letzten Teil der Artikelserie einen Überblick aufmalen. Mit diesem Wissen kann ich schließlich ein Signal an einer Oszilloskop-Sonde auswerten und unter Linux auf dem Oszilloskop darstellen.

Malen nach Zahlen

- Reverse Engineering: Signale auslesen an bunten Pins

- Den echten DDR-Bus identifizieren

- Die restlichen FPGA-Pins

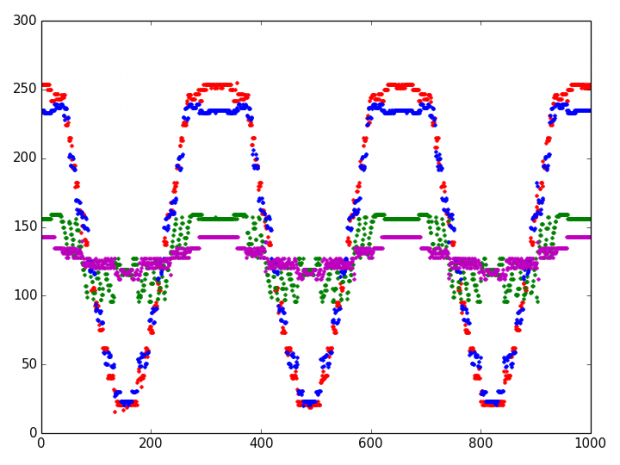

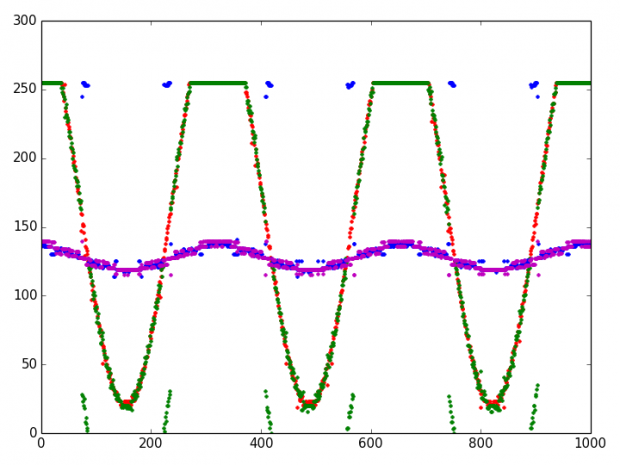

- Oszilloskop-Daten auslesen

- Die Macht der Statistik

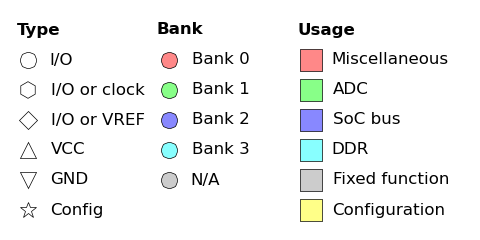

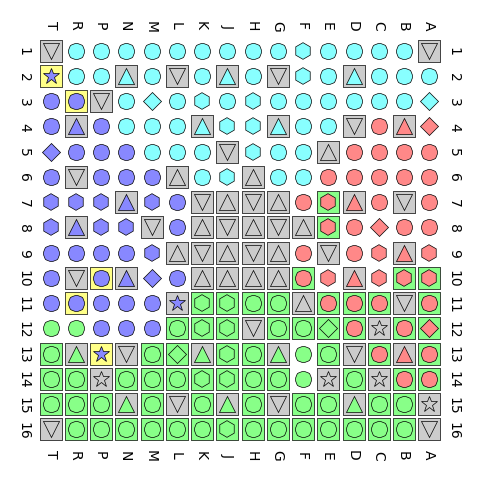

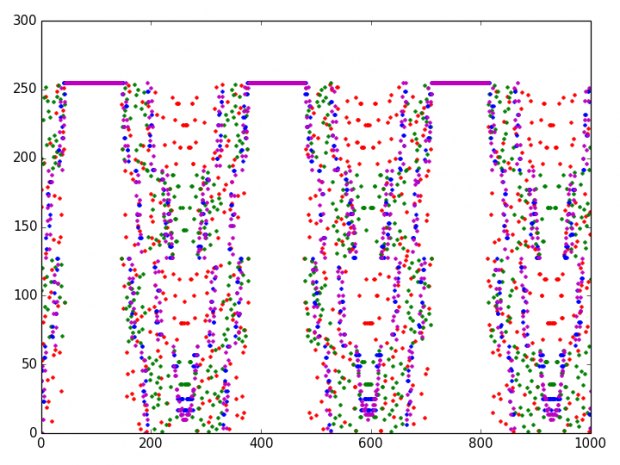

Ein FPGA hat jede Menge Pins mit unterschiedlichen Funktionen. Die Pins sind auf verschiedene I/O-Bänke aufgeteilt und können mit verschiedenen Spannungen und Standards arbeiten. Um den Überblick nicht zu verlieren, habe ich die Infos zu den Pins aus der zugehörigen Dokumentation herauskopiert und mit einem kleinen Python-Programm ein PNG erzeugt, das die Pins und ihre Nutzung anzeigt.

Die Form der Symbole zeigt die Funktion eines Pins. Ein Kreis steht für einen normalen GPIO-Pin. Pins mit einem Hexagon können entweder als GPIO-Pin oder als Takteingabe fungieren. Ein Karo steht für einen normalen GPIO-Pin oder dient als Referenzspannung (VREF), wie sie bei einigen Schnittstellenstandards erforderlich ist. Die übrigen Symbole stehen für Pins mit festgelegten Funktionen und können nicht für GPIO-Aufgaben konfiguriert werden.

Die Farbe des Symbols zeigt dessen Bank an. Die Pins für die Stromversorgung der internen Logik des FPGA und die Masse-Pins gehören keiner Bank an, sie sind grau markiert. Die farbigen Vierecke um einige Pins zeigen an, welche Funktion sie meiner Meinung nach haben. Zum Beispiel dienen die Pins mit den gelben Vierecken zur Konfiguration des FPGA. Die Farbe der Symbole für diese Pins ist Blau, daher benutzen sie die Spannungswerte von Bank 2.

Die Pins P10, R3 und T11 können nach der Konfiguration als GPIO-Pins benutzt werden. Im Gegensatz dazu kann die Konfiguration der Pins L13 und T2 nicht geändert werden. L11 und N14 werden nicht zur Konfiguration eingesetzt und sind deshalb grau. A15, C12, C14 und E14 sind JTAG-Pins, allerdings sind diese Pins anscheinend nirgendwo angebunden.

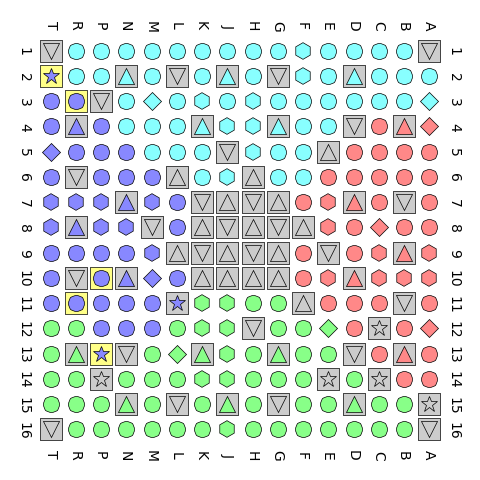

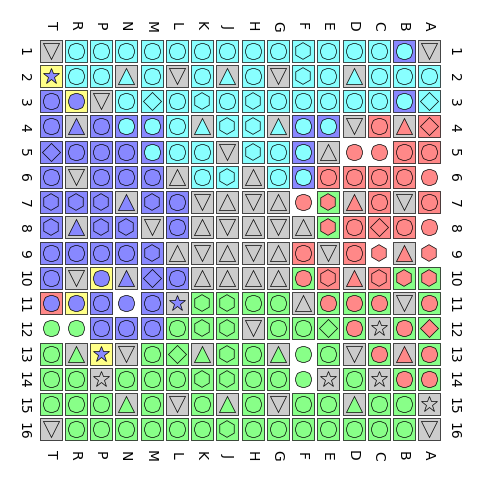

Wo der SoC-Bus anliegt

Im vorherigen Artikel habe ich eine ganze Reihe von Pins gefunden, die ständig geschaltet werden. Sie sind wohl mit dem DDR-Speicherbus des SoC verbunden. Darüber kommuniziert der SoC hauptsächlich mit dem FPGA. Dazu simuliert der FPGA einen DDR-Speicher, den der SoC ausliest oder beschreibt. Ich habe die Pins entsprechend als "SoC bus" markiert und meine Grafik neu erzeugt.

Die meisten dieser Pins befinden sich in Bank 2, aber einige auch in Bank 3. Bank 2 befindet sich auch physisch am nächsten am SoC, weshalb ihre Nutzung auch vom Platinenlayout her sinnvoll ist.

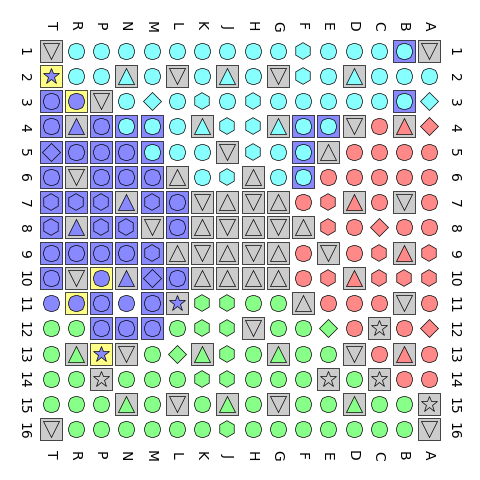

Der DDR2-Speicher benutzt den SSTL-Standard zur elektrischen Datenübertragung. Die Spannung beträgt dabei 1,8 Volt, weshalb eine externe Referenzspannung von 0,9 Volt über einen VREF-Pin benötigt wird. Ich habe einen Spannungsteiler auf der Platine gefunden, der diese Spannung bereitstellt.

An den Pins P7 und M7 liegt ein symmetrisches 133-MHz-Taktsignal vom SoC an. Noch ist mir nicht die komplette Pin-Belegung des SoC-Busses klar. Aber ich habe einige Ideen, wie ich sie herausfinden kann.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

| Den echten DDR-Bus identifizieren |

Du bist mit Abstand der coolste Typ auf dieser Erde. Wahrscheinlich wirst du eigentlich...

Jo, das Trollen bei Heise war schon mal lustiger. Früher konnte man da sicher sein, mit...