Reverse Engineering: Was ein FPGA-Baustein steuert

Den Mikrocontroller eines Oszilloskops zu analysieren, hält Fallstricke bereit. Noch schwieriger wird es bei einem verbauten FPGA. Vor allem, wenn die Entwickler eine unerwartete Idee hatten.

Es ist mir in den vorherigen drei Teilen der Artikelserie bisher gelungen, Linux auf einem Oszilloskop zu installieren und eine ganze Reihe von Pins des Mikrocontrollers und ihre Funktion herauszufinden. Doch auf der Hauptplatine des Oszilloskops befindet sich noch ein FPGA, der wahrscheinlich genauso wichtig ist. Deshalb wil ich im vierten Teil herausfinden, welche Funktionen dessen Pins haben. Im Gegensatz zum Mikrocontroller kann ich auf dem FPGA aber nicht einfach ein paar einfache Programme laufen lassen.

- Reverse Engineering: Was ein FPGA-Baustein steuert

- Hello World

- Die Auswertung wird beschleunigt

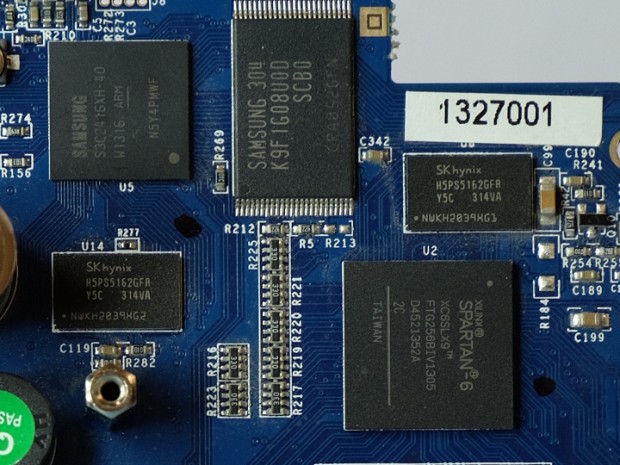

Ich habe die GPIO-Pins des SoC analysiert, indem ich sie als Eingang konfiguriert und dann an den verschiedensten Stellen auf der Platine ein Signal angelegt habe. Ein selbstgeschriebener Linux-Treiber hat mir dann den zugehörigen Pin angezeigt. Mit der gleichen Methode will ich jetzt auch die Pins des FPGA analysieren. Der FPGA im Oszilloskop ist ein Xilinx Spartan 6 XC6SLX9.

Er hat einen integrierten Speichercontroller in der Pin-Bank 3, die sich im obigen Bild am oberen Rand des FPGA befindet. Der Speichercontroller ist hoffentlich mit dem Hynix-DDR2-Speicher direkt oberhalb des FPGA verbunden. Die Pin-Bank 2 ist auf der linken Seite des FPGA und wahrscheinlich über die Widerstände mit dem SoC verbunden. Die Pin-Bank 1 befindet sich unten, viele Leiterbahnen verlaufen von dort zu den Analog-Digital-Konvertern (ADC). Die Pin-Reihe 0 liegt rechts und deren Verwendung ist nicht direkt ersichtlich. Aber das herauszufinden, ist schließlich die Idee hinter dem Reverse Engineering.

Wie die FPGA-Programmierung funktioniert

Ein FPGA ist ein programmierbarer Logikbaustein. Abhängig vom Blickwinkel hat ein FPGA entweder überhaupt nichts mit der Programmierung zu tun und ist einfach ein Stück rekonfigurierbare Hardware oder es ist ein programmierbares Ding, das mit einer sehr ungewöhnlichen Programmiersprache funktioniert.

Die Logikgatter des FPGA können direkt konfiguriert und Logikschaltungen mit AND-, OR- XOR-Gatter, Invertern, Latches und Flip-Flops aufgebaut werden. Üblicherweise wird aber eine Hardware-Beschreibungssprache (HDL) verwendet, wie zum Beispiel Verilog oder VHDL. Diese Sprachen werden auch als Registertransferebene (RTL) bezeichnet, sie abstrahieren die Abläufe in Form von Signalübertragungen zwischen Registern und logischen Operationen mit den Signalen dazwischen.

Ich habe schon früher mit Verilog herumgespielt, allerdings bin ich damit nie richtig warm geworden. Für einen Softie wie mich, also jemanden, der aus der Software-Ecke kommt, hat sich Verilog immer sehr primitiv angefühlt. Die Syntax ist ein wenig von C inspiriert, aber es ist noch systemnäher als C. Zum Beispiel hat Verilog kein Sprachenkonstrukt wie Struct. Schon einmal probiert, in C zu programmieren, ohne zusammengehörige Variablen in einem Struct zusammenfassen zu können und stattdessen jede Variable einzeln einer Funktion als Argument zu übergeben? Es gibt Verilog-Module, die Hunderte von Signalen als Argumente erwarten!

Es ist allerdings möglich, mehrere Signale in einen einzelnen großen Bitvektor zu packen. Aber das entspräche dem Verpacken eines Struct in einem Integer-Array von Hand, um es nach der Übergabe an die C-Funktion wieder von Hand zu entpacken. Das ist eine eher schmerzhafte Angelegenheit.

Systemverilog, eine Erweiterung von Verilog, soll solche Probleme lösen. Aber viele Herstellerwerkzeuge wie das kostenlose Xilinx SE von Spartan unterstützen es nicht. VHDL ist umfangreicher, es hat mit dem Entity-Konstrukt eine Entsprechung zum Struct-Konzept von C. Allerdings bin ich mit VHDL nie zurechtgekommen. Die Syntax erinnert mich an ADA und ich mag es einfach nicht.

Mit einer Hochsprache Hardware beschreiben

Da Verilog eher primitiv aufgebaut ist, haben viele bereits Werkzeuge entwickelt, um Verilog aus anderen Sprachen zu erzeugen. Vor einigen Jahren bin ich über MyHDL gestolpert, das Verilog oder VHDL aus Python-Code erzeugt. Es sah sehr interessant aus und ich wollte es schon immer einmal ausprobieren.

Ich stieß dabei auch auf Rhea. Dabei handelt es sich um eine Handvoll nützlicher Bibliotheken für MyHDL, es enthält auch eine Reihe von Build-Skripten für viele verschiedene FPGAs.

Jede Menge neue Spielzeuge, um herumzuspielen und zu lernen.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed

| Hello World |

Einsynchronisieren ist quasi im hello World für FPGA's mit drin. Alles andere ist (bis...

Wenn es um Oszilloskope geht wird idR kräftig in der Trickkiste gerührt. Schneller...

wir haben die Erfahrung gemacht, dass es Softwareleute gibt, die durchaus meinen, man...

was vielen nicht klar ist: ein fpga ist inhärent echtzeitfähig.