Cortex-A32: Dieser ARMv8-Kern ist für 32 statt 64 Bit optimiert

ARMs neuer Cortex-A32 basiert zwar auf der ARMv8-A-Technik, allerdings nutzt er einzig das Aarch32-Subset und verzichtet auf eine 64-Bit-Unterstützung. Das macht ihn bei 32-Bit-Code und Verschlüsselung besonders effizient und obendrein extrem klein.

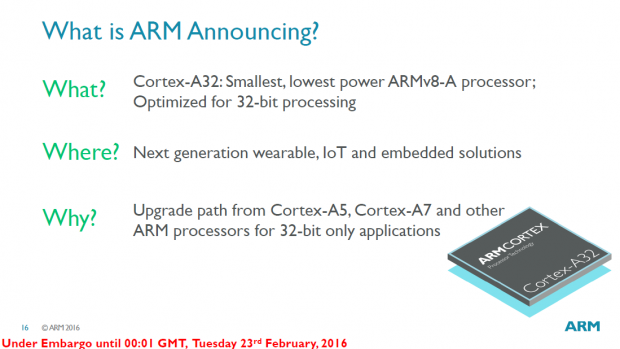

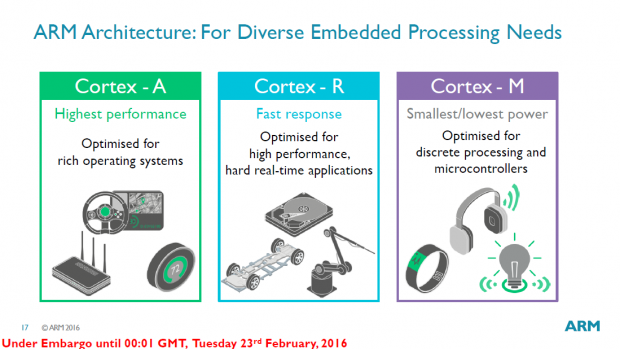

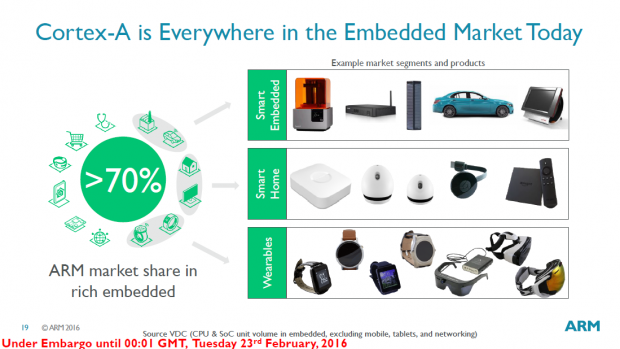

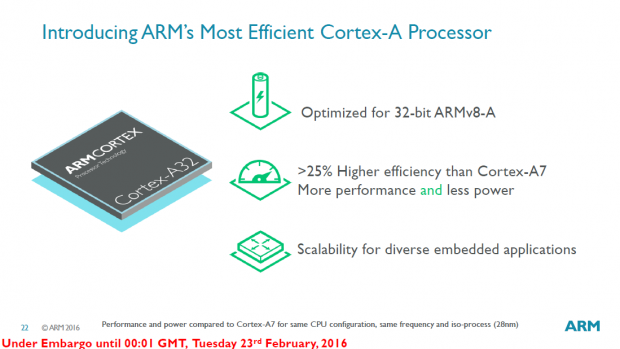

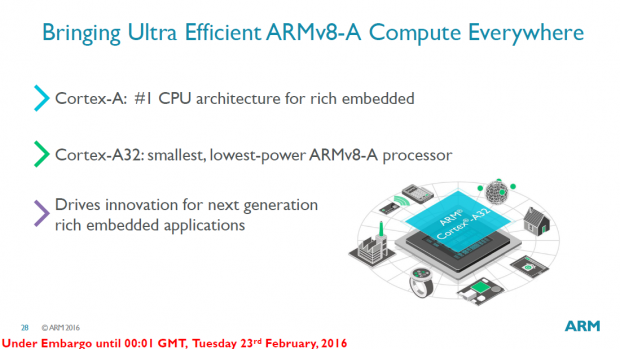

Der CPU-Entwickler ARM hat den neuen Cortex-A32 vorgestellt, den ersten Kern mit ARMv8-A-Technik, aber ohne 64-Bit-Unterstützung. Durch diese spezielle Anpassung ist er der bisher kleinste Kerne der Cortex-A-Serie und soll im sogenannten Rich-Embedded-Umfeld verwendet werden. Darunter versteht ARM Bereiche wie das Internet der Dinge und Wearables, etwa Smartwatches oder VR-Headsets, die mit diversen Betriebssystemen laufen.

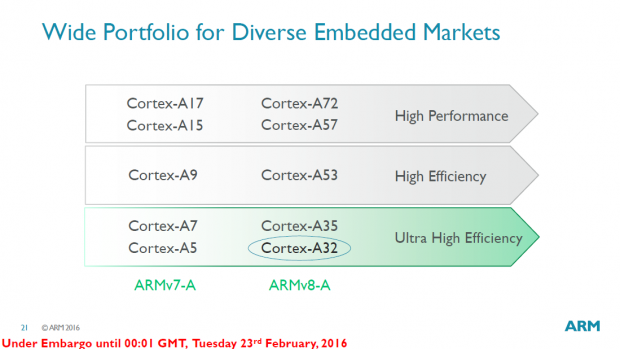

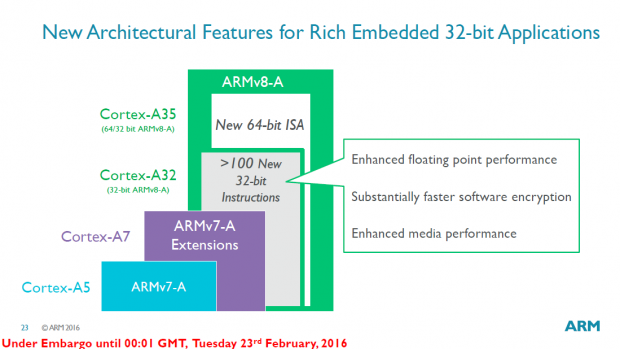

Mit dem Cortex-A32 liefert ARM einen Nachfolger für den Cortex-A5 und den Cortex-A7, beides sehr populäre ARMv7-Designs. Wie der kürzlich vorgestellte Cortex-A35 basiert auch der neue Cortex-A32 auf der ARMv8-A-Technik, ARM verzichtet jedoch auf das Aarch64-Subset und damit eine 64-Bit-Unterstützung. Stattdessen arbeitet der Cortex-A32 einzig mit dem seltener verwendeten Aarch32-Subset in 32-Bit-Umgebungen, was mehrere Vorteile hat.

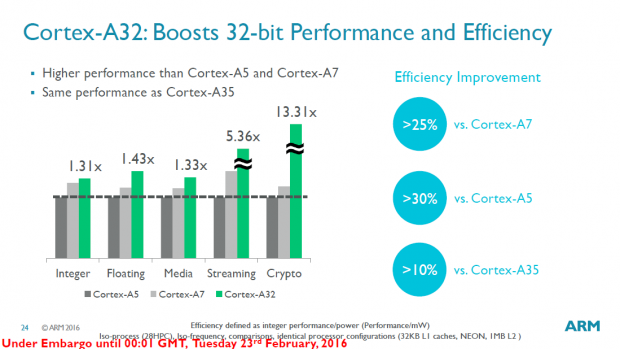

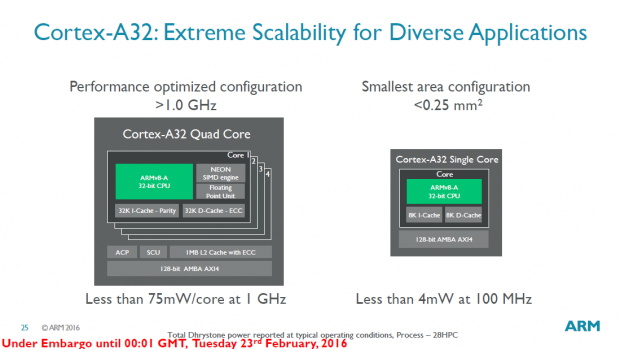

Durch das, banal ausgedrückt, Abschneiden des Aarch64-Subsets ist der Cortex-A32 besonders klein: ARM gibt für einen einzelnen Kern ohne L2-Cache eine Fläche von weniger als 0,25 mm² mit 28HPC-Fertigungsverfahren an. Verglichen mit der ARMv7 fügt die ARMv8 zudem mehr als 100 für 32 Bit gedachte Befehle hinzu, was den Cortex-A32 um den Faktor 1,3 bis 13 schneller macht als einen Cortex-A5. Die Effizienz (Integer pro Watt) steigt um über 30 Prozent, verglichen mit dem Cortex-A35 sind es rund 10 Prozent.

Wie üblich, ist auch der Cortex-A32 konfigurierbar: Die L1-Caches fassen 8 bis 32 KByte, der L2-Puffer bis zu 1 MByte. Im Vollausbau bei 1 GHz und 28HPC-Technik soll ein Kern weniger als 75 mW benötigen, wenn vier kombiniert werden. Ohne L2 und mit 8 KByte L1D/L1I bei 100 MHz spricht ARM von 4 mW.

Oder nutzen Sie das Golem-pur-Angebot

und lesen Golem.de

- ohne Werbung

- mit ausgeschaltetem Javascript

- mit RSS-Volltext-Feed